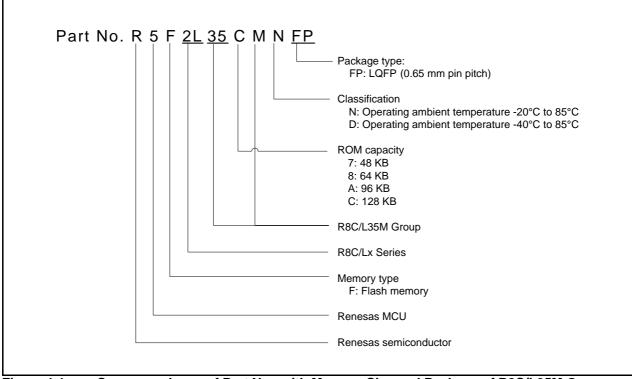

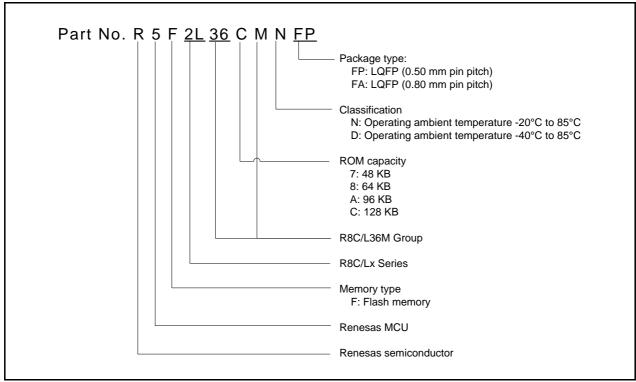

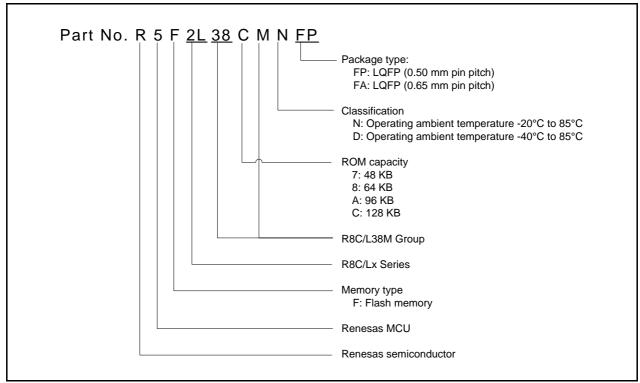

R8C/L35M Group, R8C/L36M Group, R8C/L38M Group, R8C/L3AM Group

User's Manual: Hardware

RENESAS MCU R8C Family / R8C/Lx Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

## 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

## 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# How to Use This Manual

## Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual.

The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

The following documents apply to the R8C/L35M Group, R8C/L36M Group, R8C/L38M Group, R8C/L38M Group, Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Electronics Web site.

| Document Type               | Description                                                                                                                                                                                                                                     | Document Title                                                                               | Document No.       |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------|

| Datasheet                   | Hardware overview and electrical characteristics                                                                                                                                                                                                | R8C/L35M Group, R8C/L36M Group,<br>R8C/L38M Group, R8C/L3AM Group<br>Datasheet               | R01DS0028EJ0002    |

| User's Manual:<br>Hardware  | Hardware specifications (pin assignments, memory maps, peripheral function specifications, electrical characteristics, timing charts) and operation description Note: Refer to the application notes for details on using peripheral functions. | R8C/L35M Group, R8C/L36M Group,<br>R8C/L38M Group, R8C/L3AM Group<br>User's Manual: Hardware | This User's Manual |

| User's Manual:<br>Software  | Description of CPU instruction set                                                                                                                                                                                                              | R8C/Tiny Series Software Manual                                                              | REJ09B0001         |

| Application note            | Information on using peripheral functions and application examples Sample programs Information on writing programs in assembly language and C                                                                                                   | Available from the Renesas Electron                                                          | nics Web site.     |

| Renesas<br>technical update | Product specifications, updates on documents, etc.                                                                                                                                                                                              |                                                                                              |                    |

## 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

## (1) Register Names, Bit Names, and Pin Names

Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word "register," "bit," or "pin" to distinguish the three categories.

Examples the PM03 bit in the PM0 register

P3\_5 pin, VCC pin

## (2) Notation of Numbers

The indication "b" is appended to numeric values given in binary format. However, nothing is appended to the values of single bits. The indication "h" is appended to numeric values given in hexadecimal format. Nothing is appended to numeric values given in decimal format.

Examples Binary: 11b

Hexadecimal: EFA0h Decimal: 1234

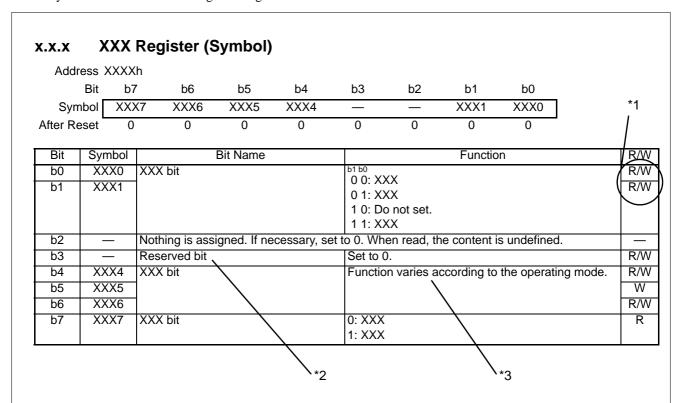

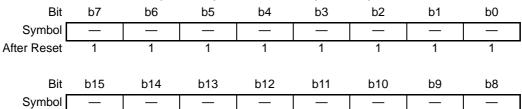

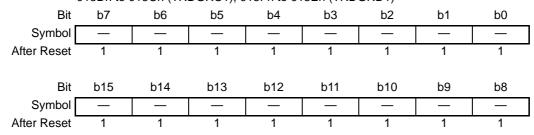

## 3. Register Notation

The symbols and terms used in register diagrams are described below.

\*1

R/W: Read and write.

R: Read only.

W: Write only.

-: Nothing is assigned.

\*2

· Reserved bit

Reserved bit. Set to specified value.

\*3

• Nothing is assigned.

Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set to a value.

Operation is not guaranteed when a value is set.

• Function varies according to the operating mode.

The function of the bit varies with the peripheral function mode. Refer to the register diagram for information on the individual modes.

# 4. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                    |

|--------------|----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter |

| bps          | bits per second                              |

| CRC          | Cyclic Redundancy Check                      |

| DMA          | Direct Memory Access                         |

| DMAC         | Direct Memory Access Controller              |

| GSM          | Global System for Mobile Communications      |

| Hi-Z         | High Impedance                               |

| IEBus        | Inter Equipment Bus                          |

| I/O          | Input/Output                                 |

| IrDA         | Infrared Data Association                    |

| LSB          | Least Significant Bit                        |

| MSB          | Most Significant Bit                         |

| NC           | Non-Connect                                  |

| PLL          | Phase Locked Loop                            |

| PWM          | Pulse Width Modulation                       |

| SIM          | Subscriber Identity Module                   |

| UART         | Universal Asynchronous Receiver/Transmitter  |

| VCO          | Voltage Controlled Oscillator                |

# **Table of Contents**

| SFR Pag | ge Reference                                               | B - 1 |

|---------|------------------------------------------------------------|-------|

| 1. O\   | verview                                                    | 1     |

| 1.1     | Features                                                   | 1     |

| 1.1.1   | Applications                                               |       |

| 1.1.2   | **                                                         |       |

| 1.1.3   | •                                                          |       |

| 1.2     | Product Lists                                              | 7     |

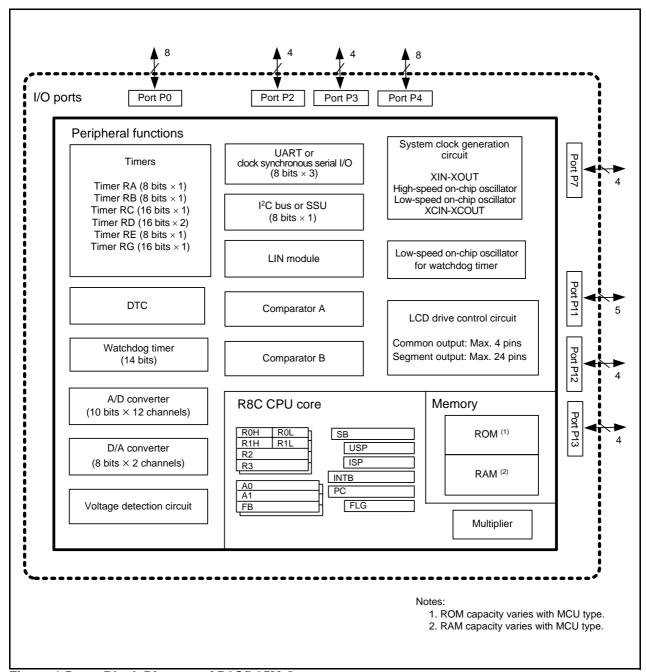

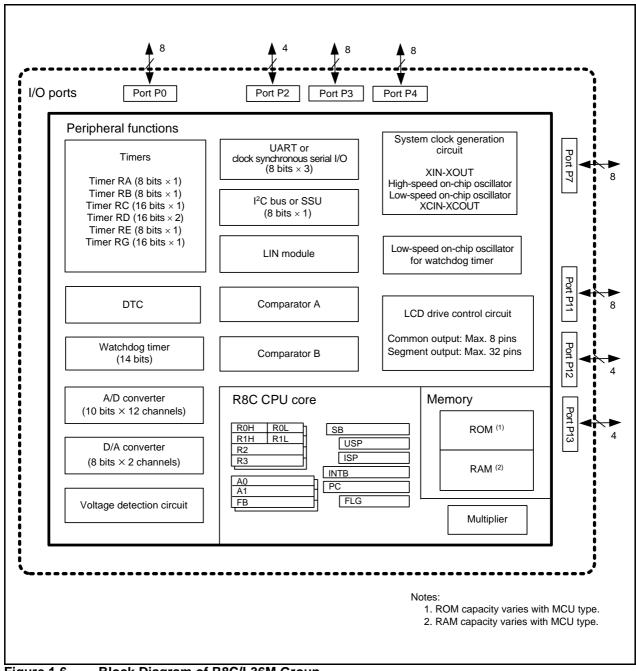

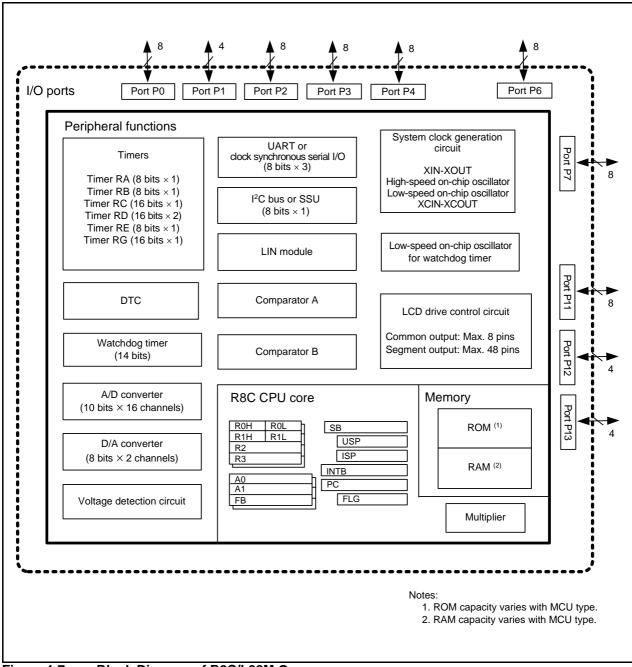

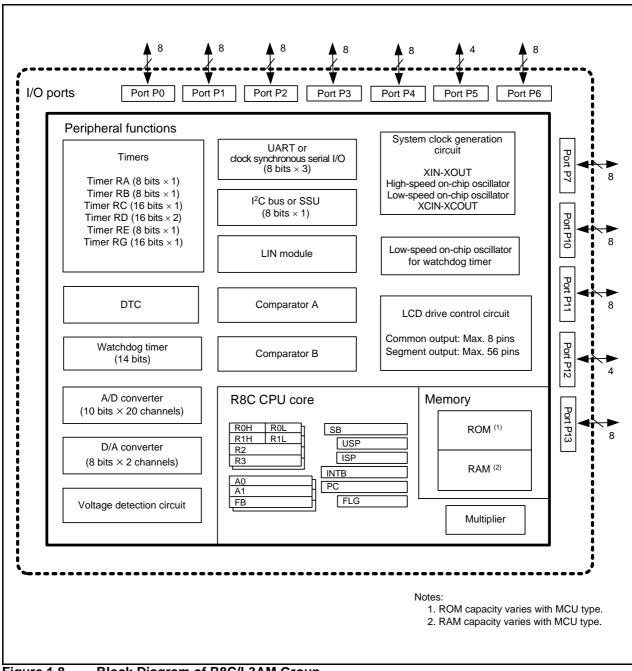

| 1.3     | Block Diagrams                                             | 11    |

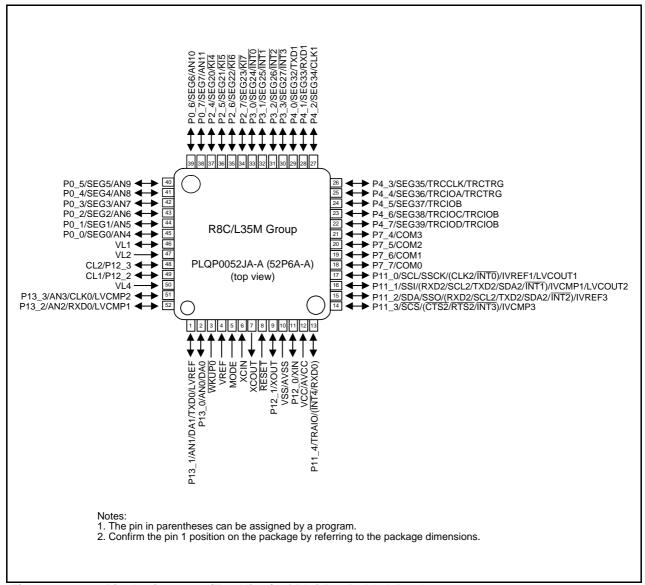

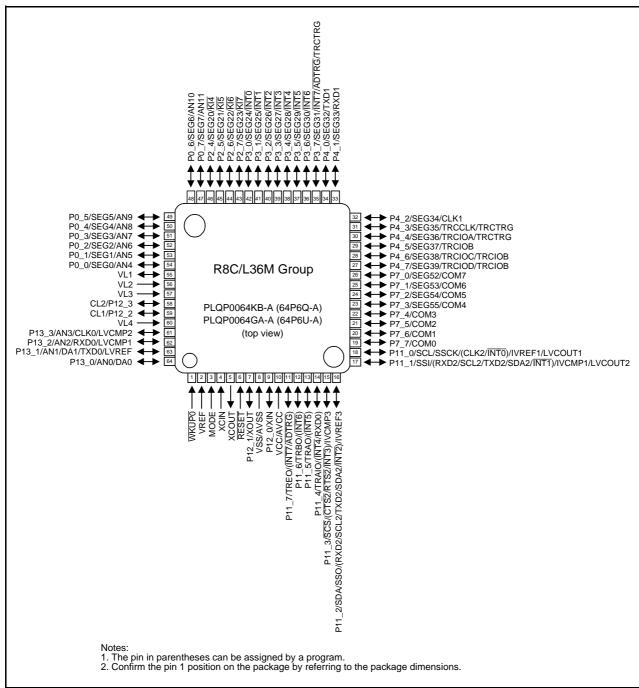

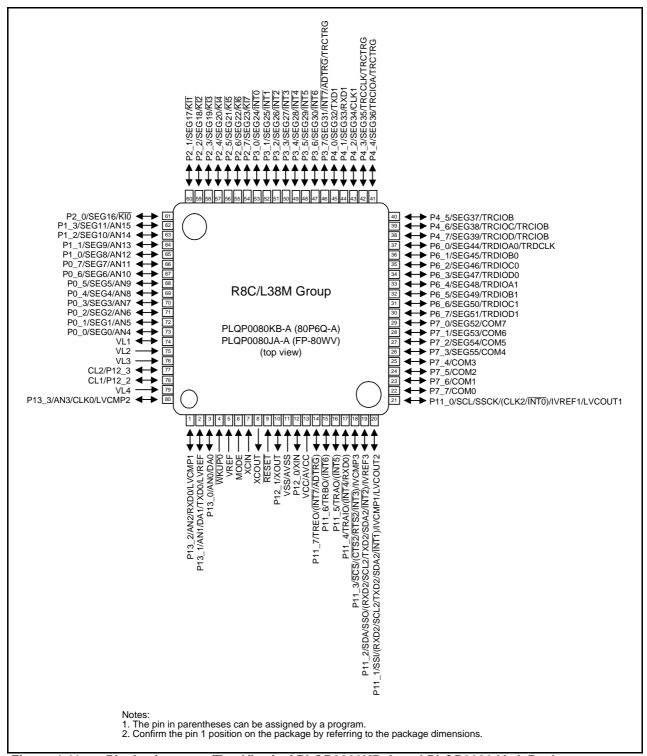

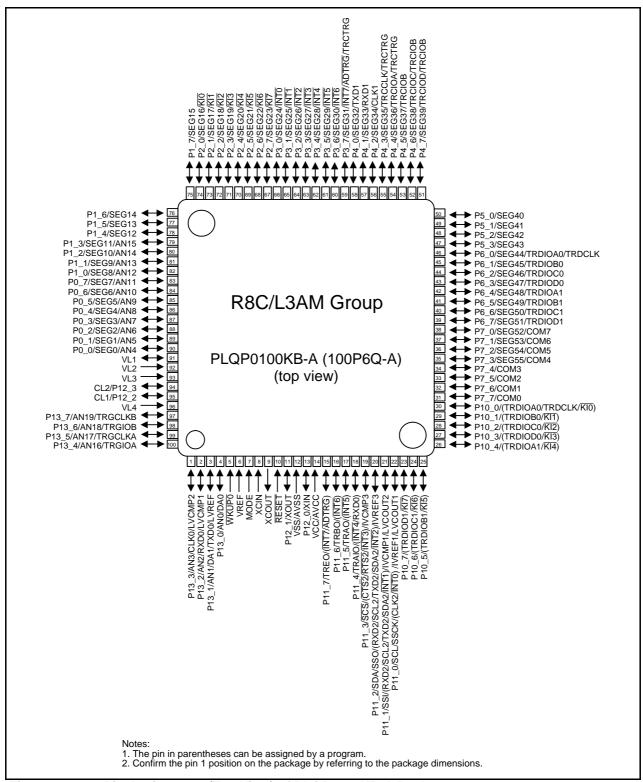

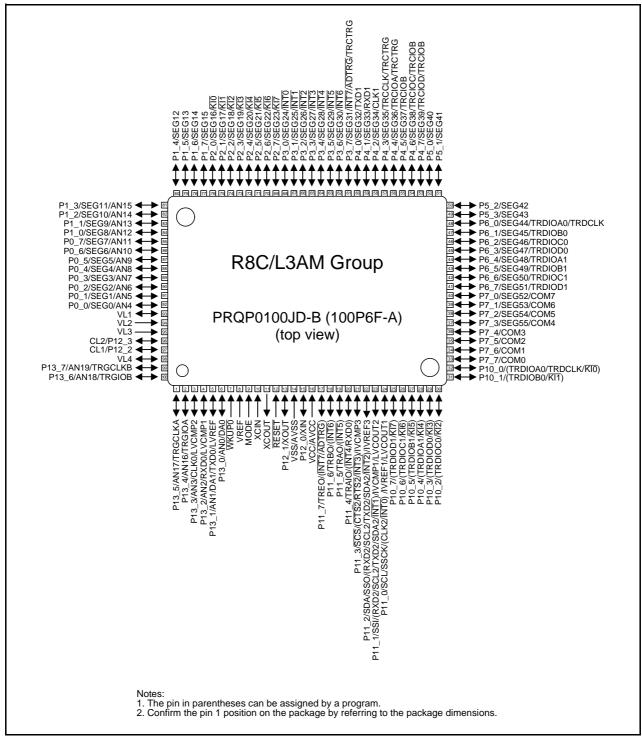

| 1.4     | Pin Assignments                                            | 15    |

| 1.5     | Pin Functions                                              | 23    |

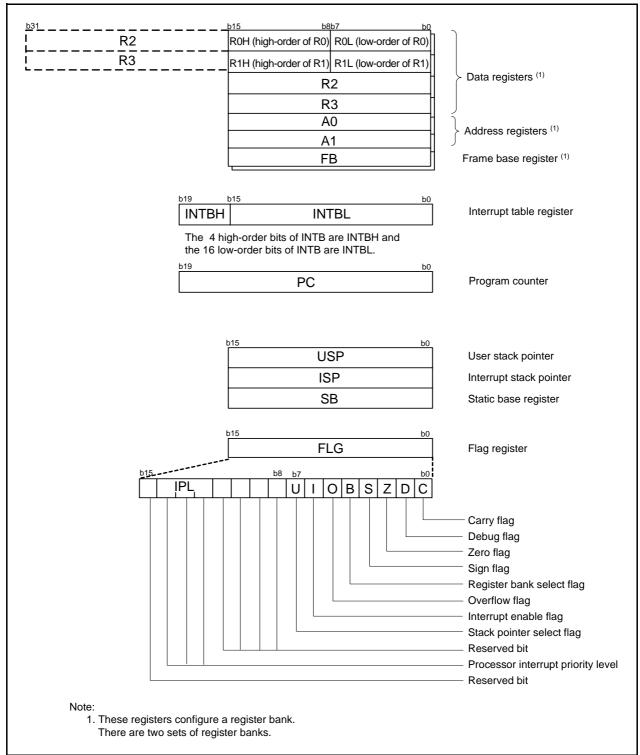

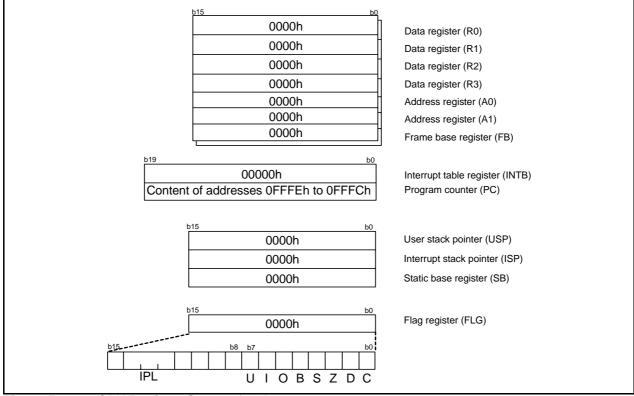

| 2. Ce   | entral Processing Unit (CPU)                               | 25    |

| 2.1     | Data Registers (R0, R1, R2, and R3)                        | 26    |

| 2.2     | Address Registers (A0 and A1)                              | 26    |

| 2.3     | Frame Base Register (FB)                                   | 26    |

| 2.4     | Interrupt Table Register (INTB)                            | 26    |

| 2.5     | Program Counter (PC)                                       | 26    |

| 2.6     | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) | 26    |

| 2.7     | Static Base Register (SB)                                  | 26    |

| 2.8     | Flag Register (FLG)                                        | 26    |

| 2.8.1   | Carry Flag (C)                                             | 26    |

| 2.8.2   | Debug Flag (D)                                             |       |

| 2.8.3   | Zero Flag (Z)                                              | 26    |

| 2.8.4   | Sign Flag (S)                                              | 26    |

| 2.8.5   | Register Bank Select Flag (B)                              |       |

| 2.8.6   | Overflow Flag (O)                                          |       |

| 2.8.7   | Interrupt Enable Flag (I)                                  | 27    |

| 2.8.8   | Stack Pointer Select Flag (U)                              | 27    |

| 2.8.9   | Processor Interrupt Priority Level (IPL)                   | 27    |

| 2.8.10  | 0 Reserved Bit                                             | 27    |

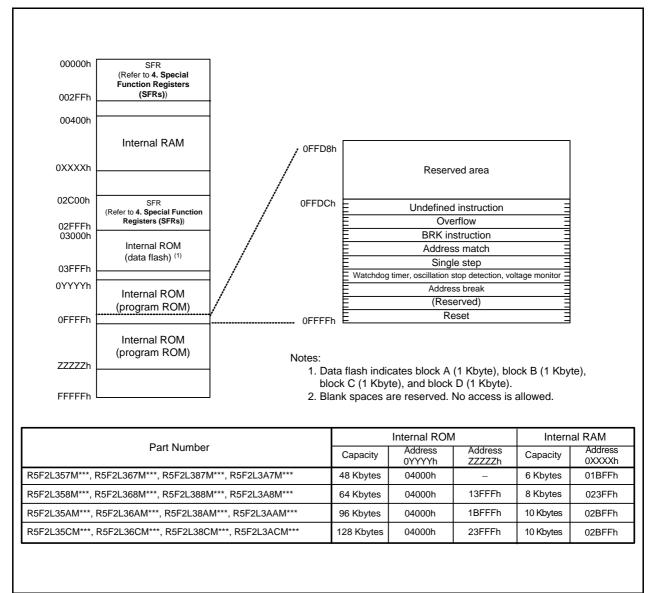

| 3. Me   | emory                                                      | 28    |

| 4. Sp   | pecial Function Registers (SFRs)                           | 29    |

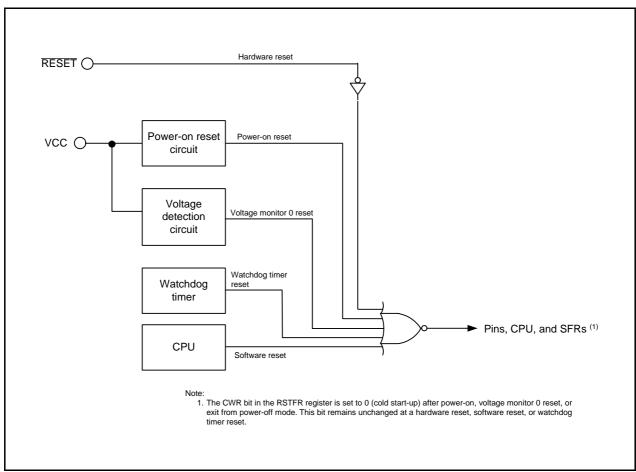

| 5. Re   | esets                                                      | 45    |

| 5.1     | Registers                                                  | 48    |

| 5.1.1   | Processor Mode Register 0 (PM0)                            |       |

| 5.1.2   | Reset Source Determination Register (RSTFR)                | 48    |

| 5.1.3   | Option Function Select Register (OFS)                      | 49    |

| 5.1.4   | Option Function Select Register 2 (OFS2)                   | 50    |

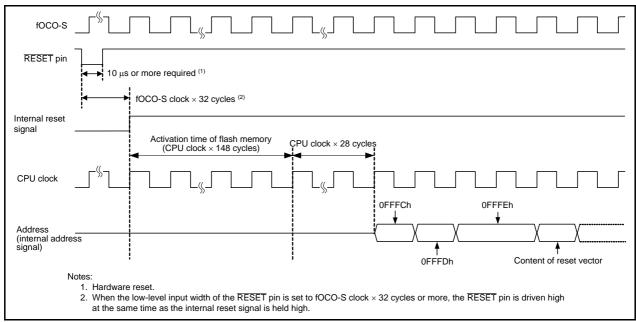

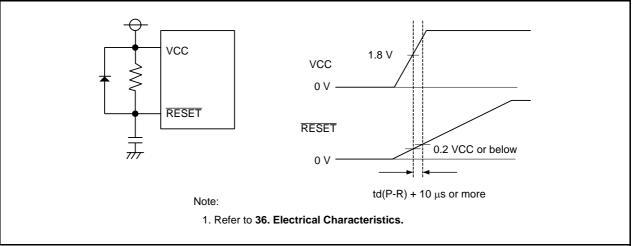

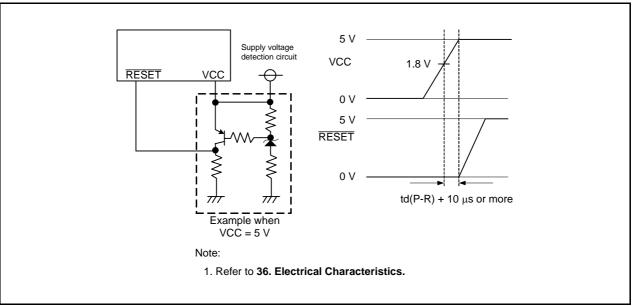

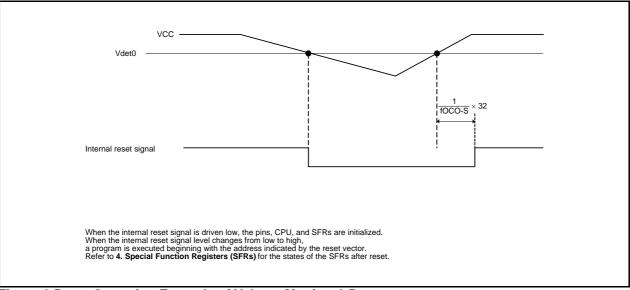

| 5.2     | Hardware Reset                                             | 51    |

| 5.2.1   | When Power Supply is Stable                                | 51    |

| 5.2.2   | Power On                                                   | 51    |

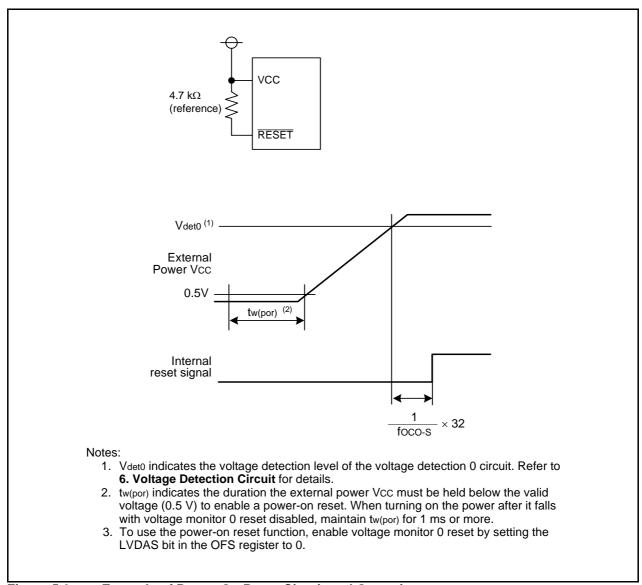

| 5.3     | Power-On Reset Function                                    | 53    |

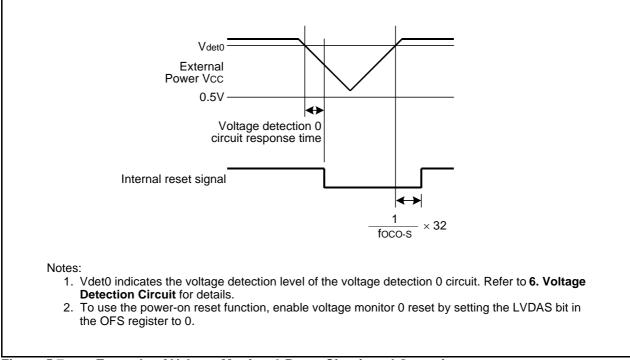

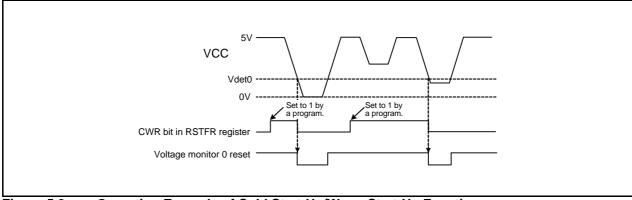

| 5.4     | Voltage Monitor 0 Reset                                    | 54    |

| 5.5     | Watchdog Timer Reset                                       | 55    |

| 5.6     | Software Reset                                             | 55    |

| 5.7           | Cold Start-Up/Warm Start-Up Determination Function              | 56 |

|---------------|-----------------------------------------------------------------|----|

| 5.8           | Reset Source Determination Function                             | 56 |

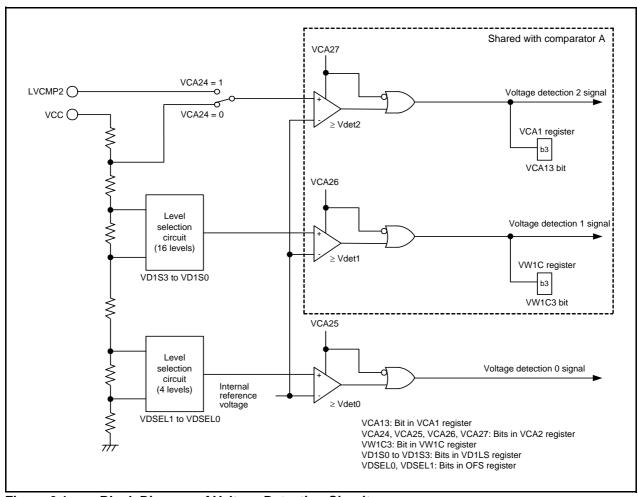

| 6. Vol        | tage Detection Circuit                                          | 57 |

| 6.1           | Introduction                                                    |    |

| 6.2           | Registers                                                       |    |

| 6.2.1         | Voltage Monitor Circuit/Comparator A Control Register (CMPA)    | 61 |

| 6.2.2         | Voltage Monitor Circuit Edge Select Register (VCAC)             | 62 |

| 6.2.3         | Voltage Detect Register 1 (VCA1)                                | 62 |

| 6.2.4         | Voltage Detect Register 2 (VCA2)                                | 63 |

| 6.2.5         | Voltage Detection 1 Level Select Register (VD1LS)               | 64 |

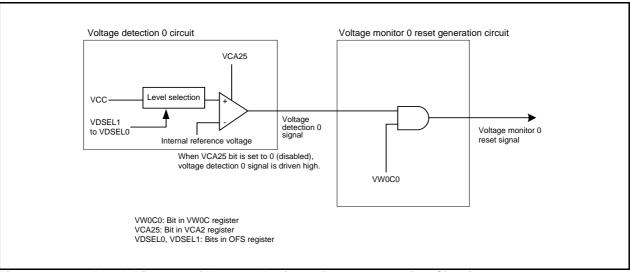

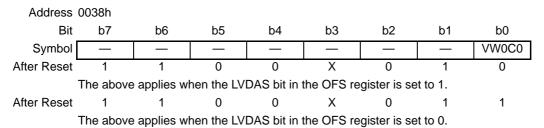

| 6.2.6         | Voltage Monitor 0 Circuit Control Register (VW0C)               | 65 |

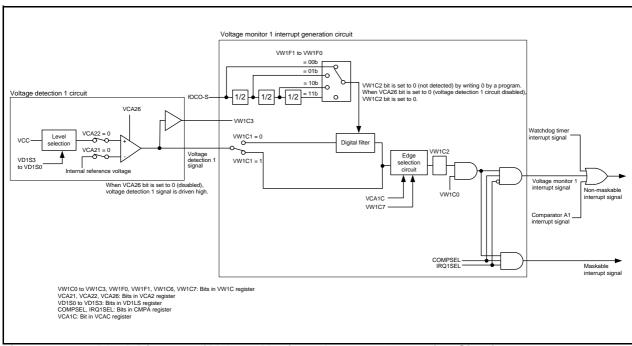

| 6.2.7         | Voltage Monitor 1 Circuit Control Register (VW1C)               | 66 |

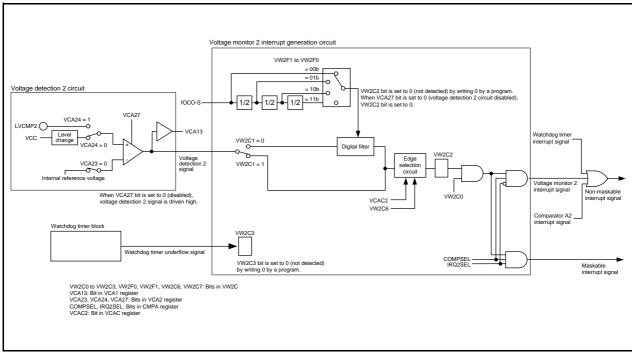

| 6.2.8         | Voltage Monitor 2 Circuit Control Register (VW2C)               | 67 |

| 6.2.9         | Option Function Select Register (OFS)                           | 68 |

| 6.3           | VCC Input Voltage                                               | 69 |

| 6.3.1         | Monitoring Vdet0                                                | 69 |

| 6.3.2         | Monitoring Vdet1                                                | 69 |

| 6.3.3         | Monitoring Vdet2                                                | 69 |

| 6.4           | Voltage Monitor 0 Reset                                         | 70 |

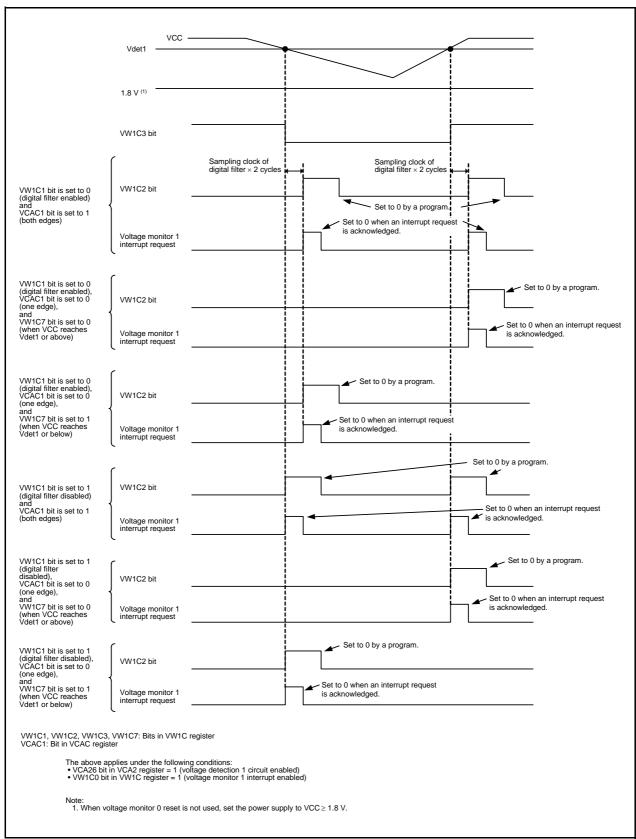

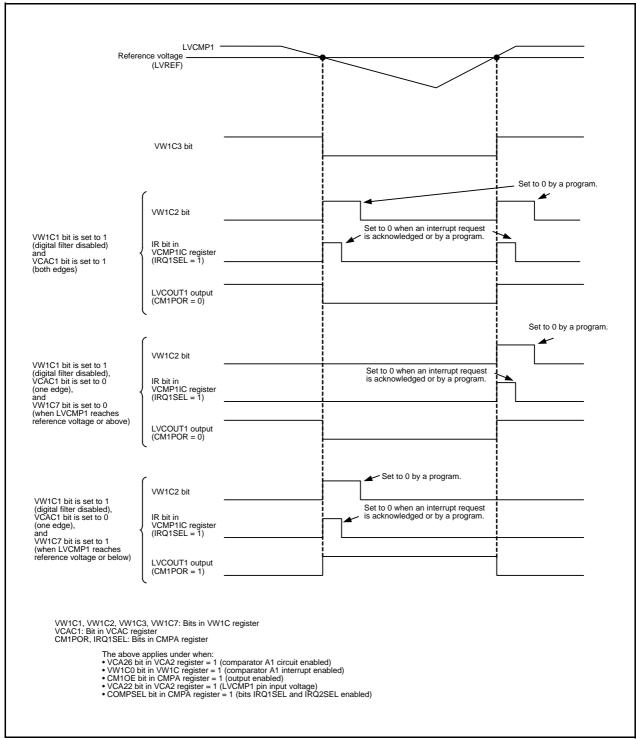

| 6.5           | Voltage Monitor 1 Interrupt                                     | 71 |

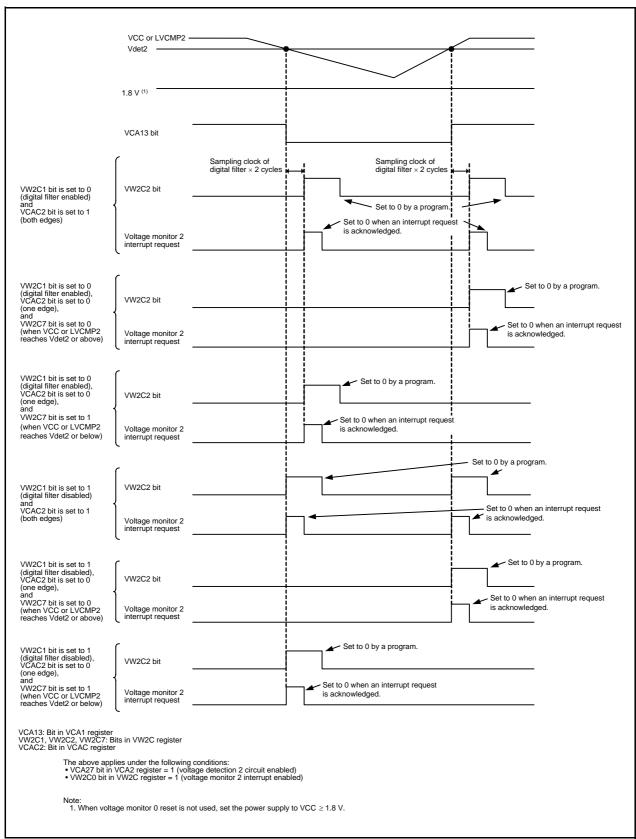

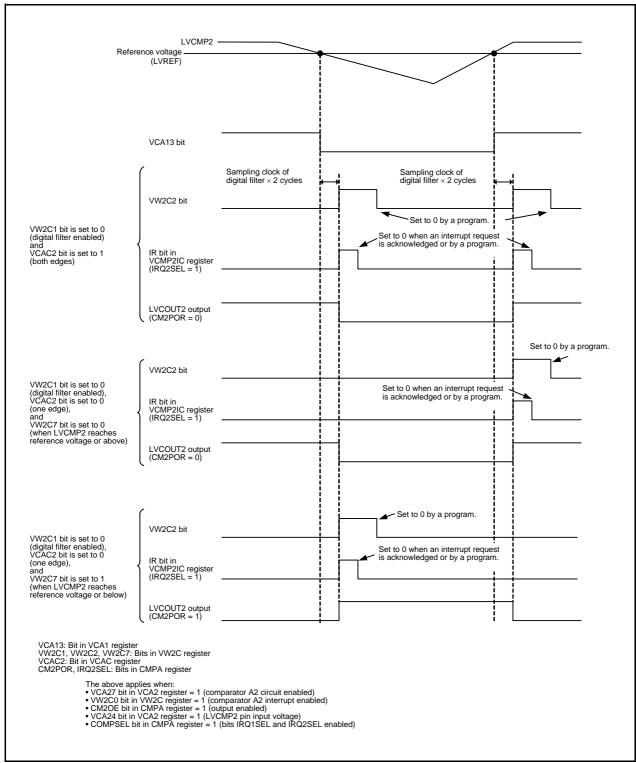

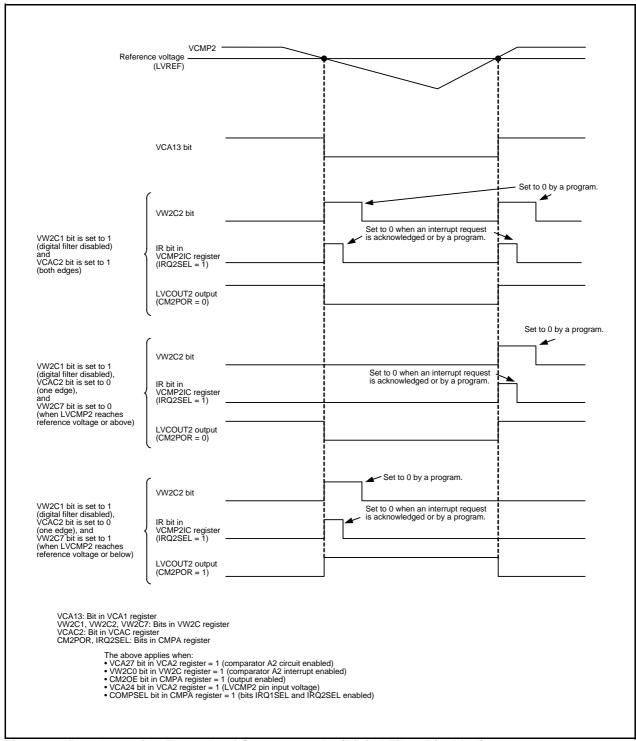

| 6.6           | Voltage Monitor 2 Interrupt                                     | 73 |

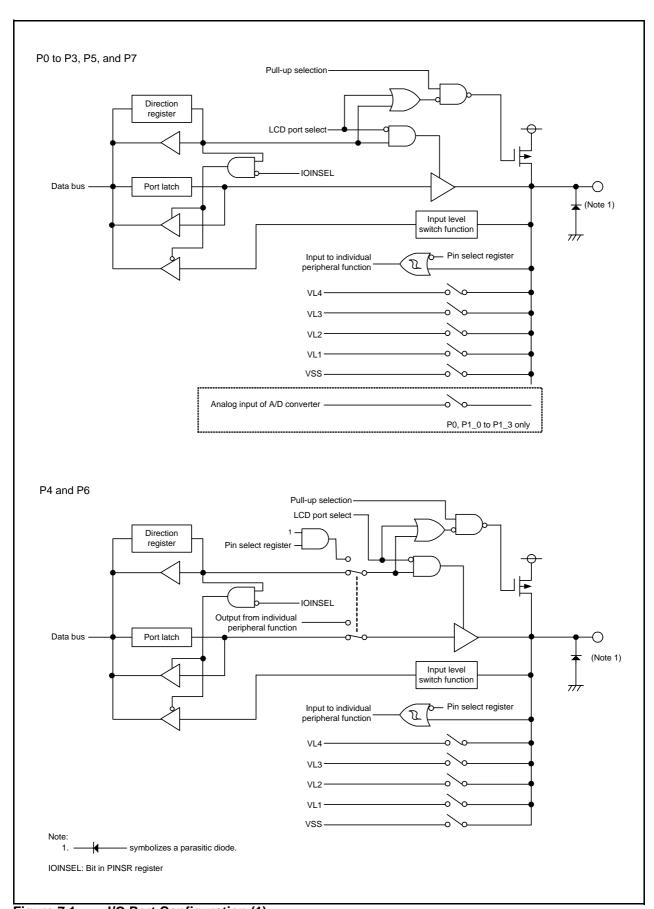

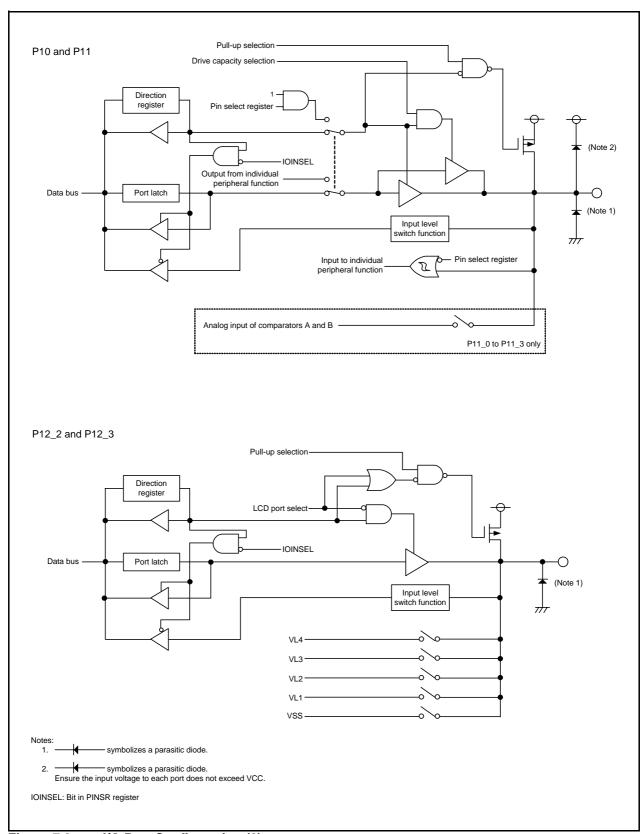

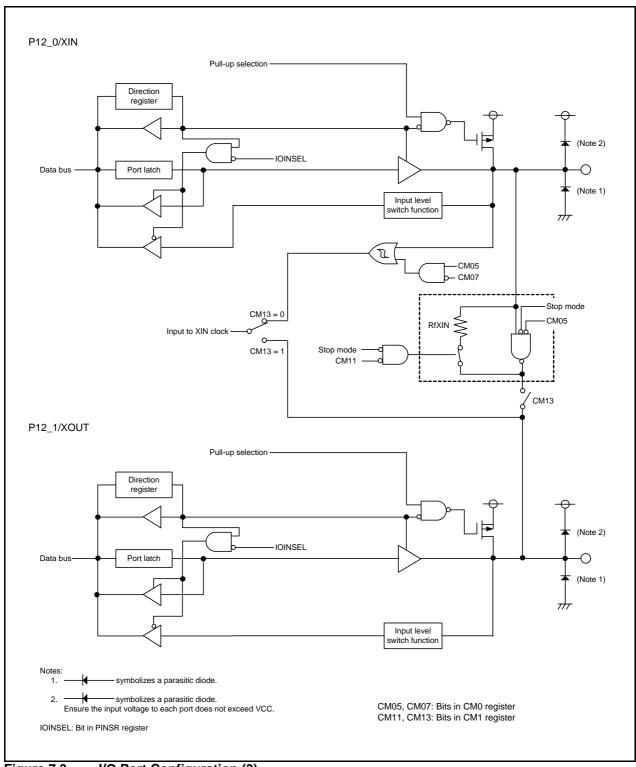

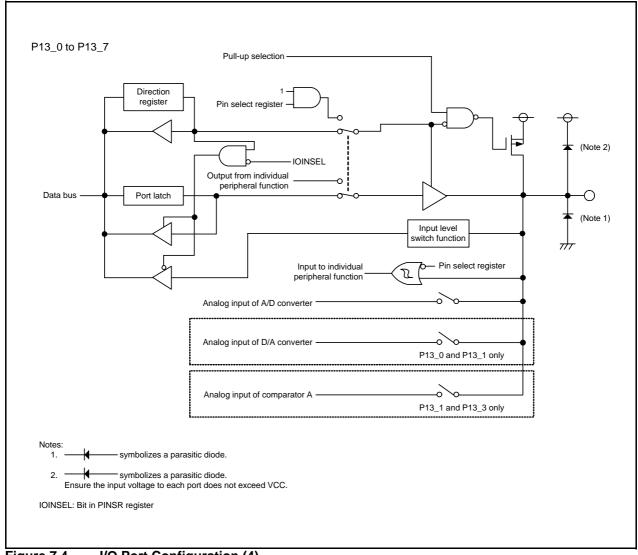

| 7. I/O        | Ports                                                           | 75 |

| 7. 1/O<br>7.1 | Introduction                                                    |    |

| 7.1<br>7.2    | I/O Port Functions                                              |    |

| 7.2           | Effect on Peripheral Functions                                  |    |

| 7.3<br>7.4    | Pins Other than I/O Ports                                       |    |

| 7.5           | Registers                                                       |    |

| 7.5.1         | Port Pi Direction Register (PDi) (i = 0 to 7, 10 to 13)         |    |

| 7.5.2         | Port Pi Register (Pi) (i = 0 to 7, 10 to 13)                    |    |

| 7.5.3         | Timer RA Pin Select Register (TRASR)                            |    |

| 7.5.4         | Timer RB/RC Pin Select Register (TRBRCSR)                       |    |

| 7.5.5         | Timer RC Pin Select Register 0 (TRCPSR0)                        |    |

| 7.5.6         | Timer RC Pin Select Register 1 (TRCPSR1)                        |    |

| 7.5.7         | Timer RD Pin Select Register 0 (TRDPSR0)                        |    |

| 7.5.8         | Timer RD Pin Select Register 1 (TRDPSR1)                        |    |

| 7.5.9         | Timer RG Pin Select Register (TRGPSR)                           |    |

| 7.5.10        | UART0 Pin Select Register (U0SR)                                | 90 |

| 7.5.11        | UART1 Pin Select Register (U1SR)                                | 91 |

| 7.5.12        | UART2 Pin Select Register 0 (U2SR0)                             | 92 |

| 7.5.13        | UART2 Pin Select Register 1 (U2SR1)                             | 92 |

| 7.5.14        | SSU/IIC Pin Select Register (SSUIICSR)                          | 93 |

| 7.5.15        | Key Input Pin Select Register (KISR)                            | 93 |

| 7.5.16        | INT Interrupt Input Pin Select Register (INTSR)                 | 94 |

| 7.5.17        | I/O Function Pin Select Register (PINSR)                        | 95 |

| 7.5.18        | Port Pi Pull-Up Control Register (PiPUR) (i = 0 to 7, 10 to 13) | 96 |

| 7.5.19        | Port P10 Drive Capacity Control Register (P10DRR)               | 97 |

| 7 5 20        | Port P11 Drive Canacity Control Register (P11DRR)               | 97 |

| ,   | 7.5.21 | Input Threshold Control Register 0 (VLT0)               | 98  |

|-----|--------|---------------------------------------------------------|-----|

| ,   | 7.5.22 | Input Threshold Control Register 1 (VLT1)               | 99  |

| ,   | 7.5.23 | Input Threshold Control Register 2 (VLT2)               | 100 |

| 7.6 | 5      | Port Settings                                           | 101 |

| 7.7 | 7      | Unassigned Pin Handling                                 | 119 |

| 8.  | Bus    | S                                                       | 120 |

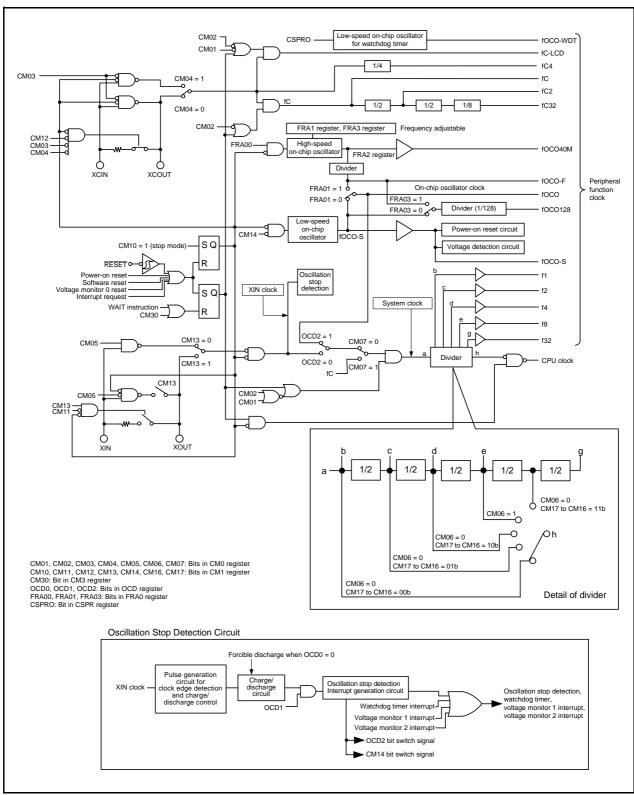

| 9.  | Clo    | ck Generation Circuit                                   | 121 |

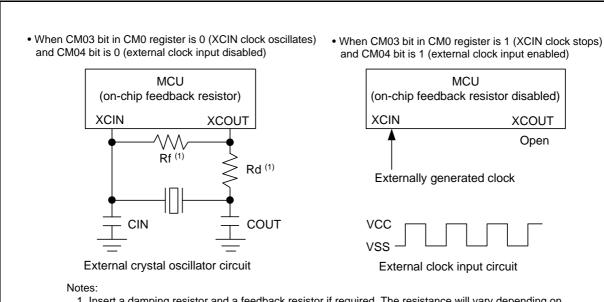

| 9.1 | 1      | Introduction                                            | 121 |

| 9.2 | 2      | Registers                                               | 124 |

| 9   | 9.2.1  | System Clock Control Register 0 (CM0)                   | 124 |

| 9   | 9.2.2  | System Clock Control Register 1 (CM1)                   | 125 |

| 9   | 9.2.3  | System Clock Control Register 3 (CM3)                   | 126 |

| 9   | 9.2.4  | Oscillation Stop Detection Register (OCD)               | 127 |

| 9   | 9.2.5  | High-Speed On-Chip Oscillator Control Register 7 (FRA7) | 128 |

| 9   | 9.2.6  | High-Speed On-Chip Oscillator Control Register 0 (FRA0) | 129 |

| 9   | 9.2.7  | High-Speed On-Chip Oscillator Control Register 1 (FRA1) | 129 |

| 9   | 9.2.8  | High-Speed On-Chip Oscillator Control Register 2 (FRA2) | 130 |

| 9   | 9.2.9  | High-Speed On-Chip Oscillator Control Register 4 (FRA4) | 131 |

| 9   | 9.2.10 | High-Speed On-Chip Oscillator Control Register 5 (FRA5) | 131 |

| 9   | 9.2.11 | High-Speed On-Chip Oscillator Control Register 6 (FRA6) | 132 |

| 9   | 9.2.12 | High-Speed On-Chip Oscillator Control Register 3 (FRA3) |     |

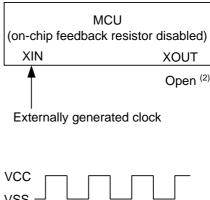

| 9.3 | 3      | XIN Clock                                               | 133 |

| 9.4 | 4      | On-Chip Oscillator Clock                                |     |

| 9   | 9.4.1  | Low-Speed On-Chip Oscillator Clock                      |     |

| 9   | 9.4.2  | High-Speed On-Chip Oscillator Clock                     |     |

| 9.5 | 5      | XCIN Clock                                              |     |

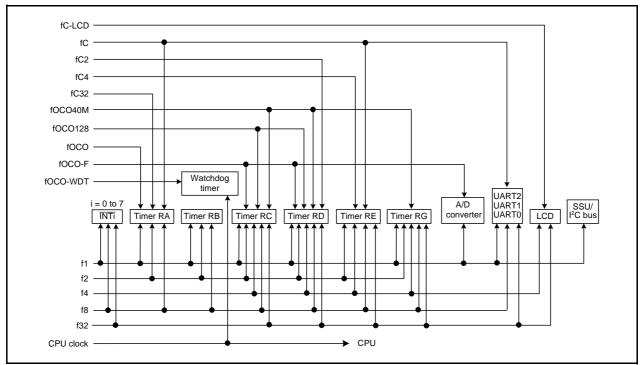

| 9.6 | 5      | CPU Clock and Peripheral Function Clock                 | 136 |

| 9   | 9.6.1  | System Clock                                            | 136 |

| 9   | 9.6.2  | CPU Clock                                               | 136 |

| 9   | 9.6.3  | Peripheral Function Clock (f1, f2, f4, f8, and f32)     | 136 |

| 9   | 9.6.4  | fOCO                                                    | 136 |

| 9   | 9.6.5  | fOCO40M                                                 | 136 |

| 9   | 9.6.6  | fOCO-F                                                  | 136 |

| 9   | 9.6.7  | fOCO-S                                                  |     |

| 9   | 9.6.8  | fOCO128                                                 | 137 |

| 9   | 9.6.9  | fC-LCD                                                  | 137 |

| 9   | 9.6.10 | fC, fC2, fC4, and fC32                                  | 137 |

| 9   | 9.6.11 | fOCO-WDT                                                | 137 |

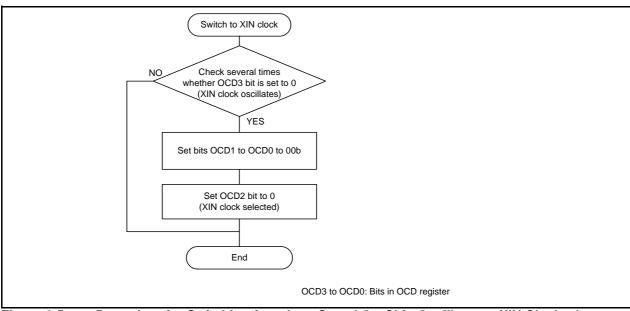

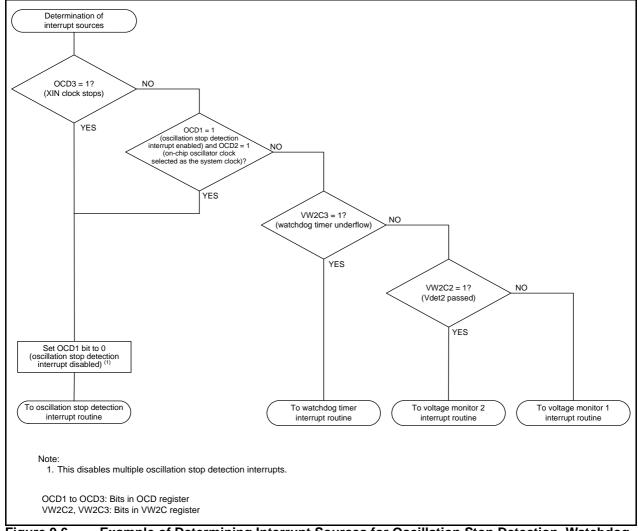

| 9.7 | 7      | Oscillation Stop Detection Function                     | 138 |

| 9   | 9.7.1  | How to Use Oscillation Stop Detection Function          | 138 |

| 9.8 | 3      | Notes on Clock Generation Circuit                       | 140 |

| 9   | 9.8.1  | Oscillation Stop Detection Function                     | 140 |

| 9   | 9.8.2  | Oscillation Circuit Constants                           | 140 |

| 9   | 9.8.3  | XCIN Clock                                              | 140 |

| 9   | 9.8.4  | Notes on Using Pins P12_0 and P12_1                     | 140 |

| 9   | 9.8.5  | High-Speed On-chip Oscillator Mode                      |     |

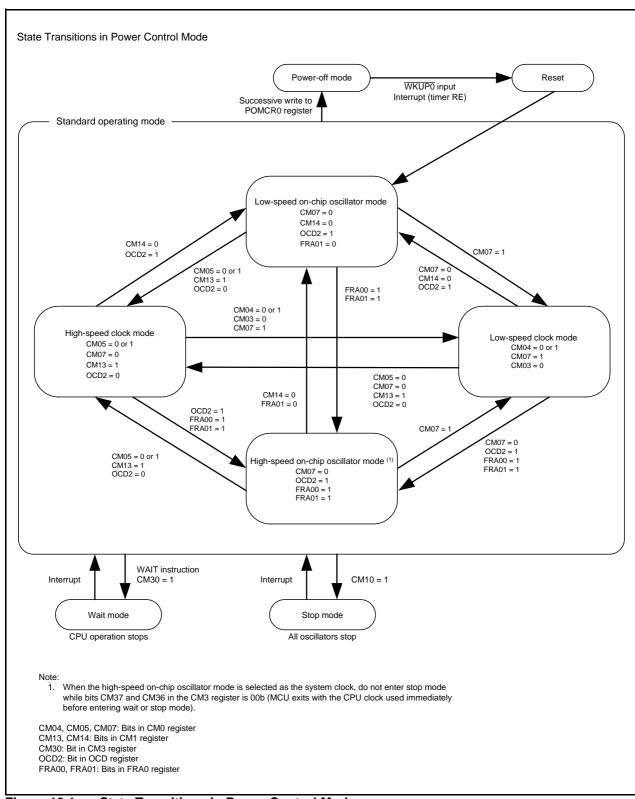

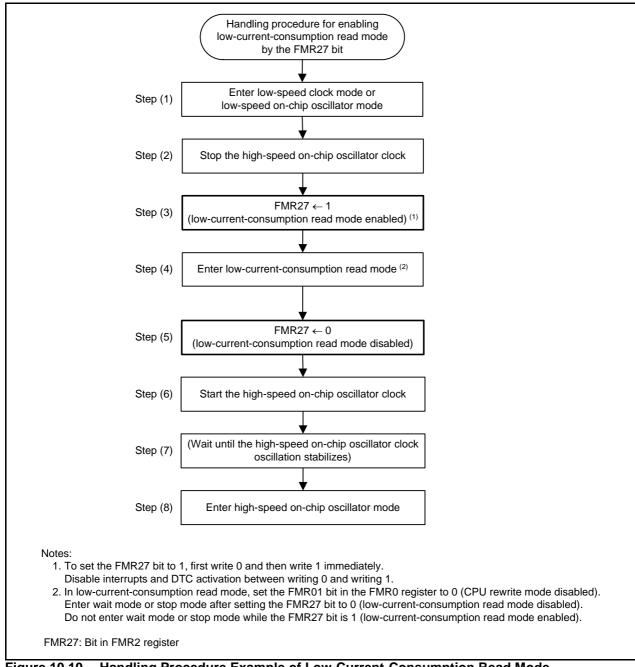

| 10.  | Pow          | er Control                                                                          | 141 |

|------|--------------|-------------------------------------------------------------------------------------|-----|

| 10.1 |              | Introduction                                                                        | 141 |

| 10.2 |              | Registers                                                                           | 143 |

| 10.  | .2.1         | System Clock Control Register 0 (CM0)                                               | 143 |

| 10.  | .2.2         | System Clock Control Register 1 (CM1)                                               |     |

| 10.  | .2.3         | System Clock Control Register 3 (CM3)                                               |     |

| 10.  | .2.4         | Oscillation Stop Detection Register (OCD)                                           |     |

|      | .2.5         | High-Speed On-Chip Oscillator Control Register 0 (FRA0)                             |     |

| 10.  | .2.6         | Voltage Detect Register 2 (VCA2)                                                    |     |

| 10.  | .2.7         | Power-Off Mode Control Register 0 (POMCR0)                                          |     |

| 10.3 |              | Standard Operating Mode                                                             |     |

| 10   | .3.1         | High-Speed Clock Mode                                                               |     |

| 10   | .3.2         | Low-Speed Clock Mode                                                                |     |

|      | .3.3         | High-Speed On-Chip Oscillator Mode                                                  |     |

|      | .3.4         | Low-Speed On-Chip Oscillator Mode                                                   |     |

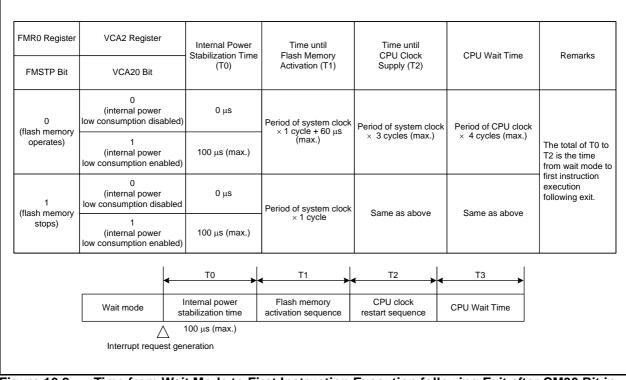

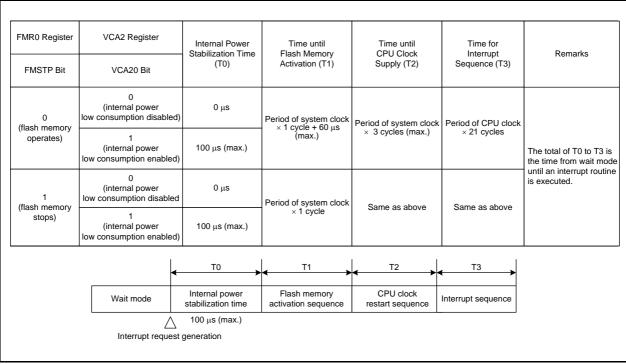

| 10.4 |              | Wait Mode                                                                           |     |

|      | .4.1         | Peripheral Function Clock Stop Function                                             |     |

|      | .4.2         | Entering Wait Mode                                                                  |     |

|      | .4.3         | Reducing Internal Power Using VCA20 Bit                                             |     |

|      | .4.4         | Pin Status in Wait Mode                                                             |     |

|      | .4.5         | Exiting Wait Mode                                                                   |     |

|      | .4.6         | Exiting Wait Mode after CM30 Bit in CM3 Register is Set to 1 (MCU Enters Wait Mode) |     |

|      | .4.7         | Exiting Wait Mode after WAIT Instruction is Executed                                |     |

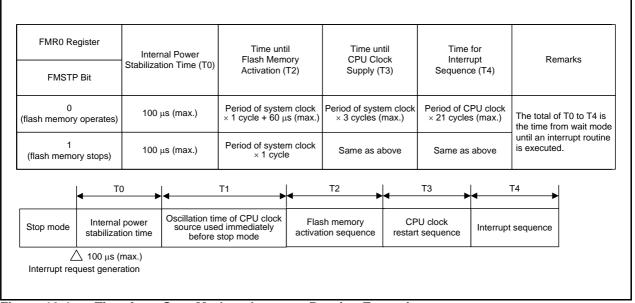

| 10.5 |              | Stop Mode                                                                           |     |

|      | .5.1         | Entering Stop Mode                                                                  |     |

|      | .5.1         | Pin Status in Stop Mode                                                             |     |

|      | .5.2         | Exiting Stop Mode                                                                   |     |

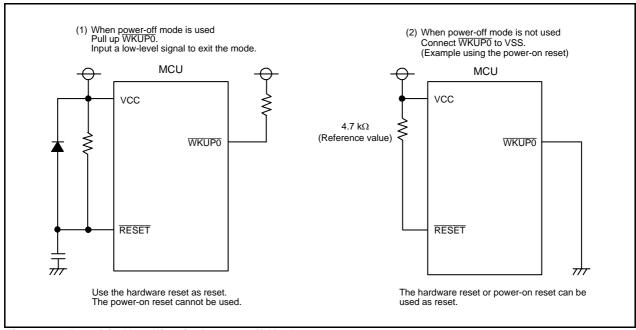

| 10.6 |              | Power-Off Mode                                                                      |     |

|      | .6.1         | Pin Handling in Power-Off Mode                                                      |     |

|      |              | Entering Power-Off Mode                                                             |     |

|      | .6.2         | Pin Status in Power-Off Mode                                                        |     |

|      |              | Exiting Power-Off Mode                                                              |     |

| 10.7 | .6.4         |                                                                                     |     |

|      |              | Reducing Power Consumption                                                          |     |

|      | .7.1<br>.7.2 | Ports                                                                               |     |

|      | .7.2         |                                                                                     |     |

|      | .7.3<br>.7.4 | Clocks                                                                              |     |

|      | .7.4         | Stopping Peripheral Function Clocks                                                 |     |

|      |              |                                                                                     |     |

|      | .7.6         | Timers                                                                              |     |

|      | .7.7         | A/D Converter                                                                       |     |

|      | .7.8         | Clock Synchronous Serial Interface                                                  |     |

|      | .7.9         | Reducing Internal Power Consumption Using VCA20 Bit                                 |     |

|      | .7.10        | 11 0                                                                                |     |

|      | .7.11        | •                                                                                   |     |

| 10.8 |              | Notes on Power Control                                                              |     |

|      | .8.1         | Stop Mode                                                                           |     |

|      | .8.2         | Wait Mode                                                                           |     |

|      | .8.3         | Reducing Internal Power Using VCA20 Bit                                             |     |

| 1()  | 84           | Power-Off Mode                                                                      | 166 |

| 10.8.  | 5 High-Speed On-chip Oscillator Mode                                                                                                                                                     | 166   |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 11. Pi | rotection                                                                                                                                                                                | . 167 |

| 11.1   | Register                                                                                                                                                                                 | 167   |

| 11.1.  |                                                                                                                                                                                          |       |

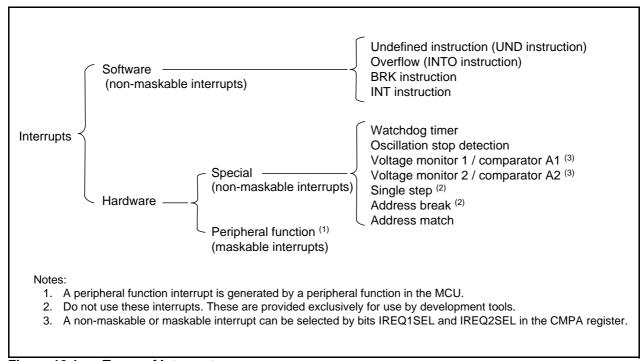

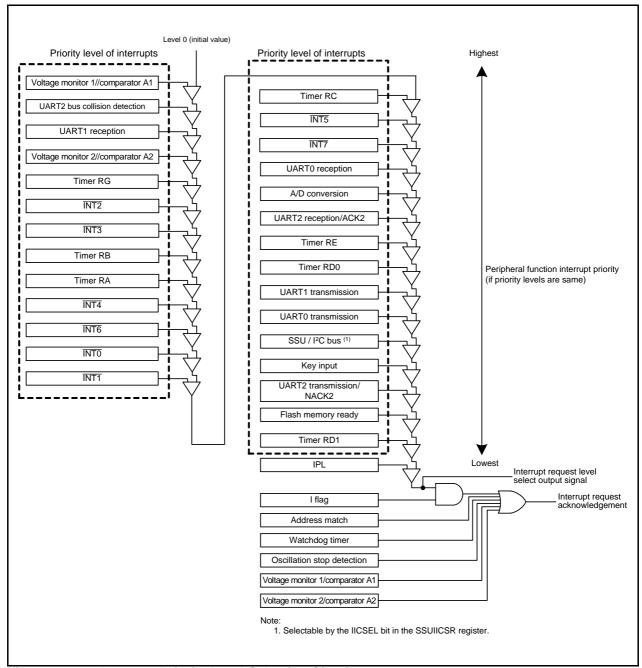

| 12. In | terrupts                                                                                                                                                                                 | . 168 |

| 12.1   | Introduction                                                                                                                                                                             | 168   |

| 12.1.  | 1 Types of Interrupts                                                                                                                                                                    | 168   |

| 12.1.  | 2 Software Interrupts                                                                                                                                                                    | 169   |

| 12.1.  | 3 Special Interrupts                                                                                                                                                                     | 170   |

| 12.1.  | 4 Peripheral Function Interrupts                                                                                                                                                         | 170   |

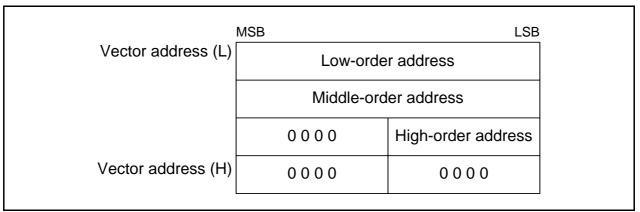

| 12.1.  | 5 Interrupts and Interrupt Vectors                                                                                                                                                       | 171   |

| 12.2   | Registers                                                                                                                                                                                | 173   |

| 12.2.  | 1 Interrupt Control Register (TREIC, S2TIC, S2RIC, KUPIC, ADIC, S0TIC, S0RIC, S1TIC, S1RIC, TRAIC, TRBIC, U2BCNIC, VCMP1IC, VCMP2IC)                                                     | 173   |

| 12.2.  | 2 Interrupt Control Register (FMRDYIC, TRCIC, TRD0IC, TRD1IC, SSUIC/IICIC, TRGIC)                                                                                                        | 174   |

| 12.2.  | 3 INTi Interrupt Control Register (INTiIC) (i = 0 to 7)                                                                                                                                  | 175   |

| 12.3   | Interrupt Control                                                                                                                                                                        | 176   |

| 12.3.  | 1 I Flag                                                                                                                                                                                 | 176   |

| 12.3.  | 2 IR Bit                                                                                                                                                                                 | 176   |

| 12.3.  | 3 Bits ILVL2 to ILVL0, IPL                                                                                                                                                               | 176   |

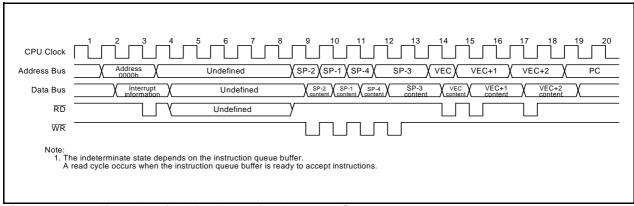

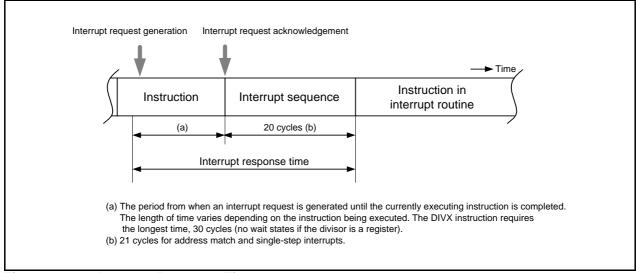

| 12.3.  | 4 Interrupt Sequence                                                                                                                                                                     | 177   |

| 12.3.  | 5 Interrupt Response Time                                                                                                                                                                | 178   |

| 12.3.  | 6 IPL Change when Interrupt Request is Acknowledged                                                                                                                                      | 178   |

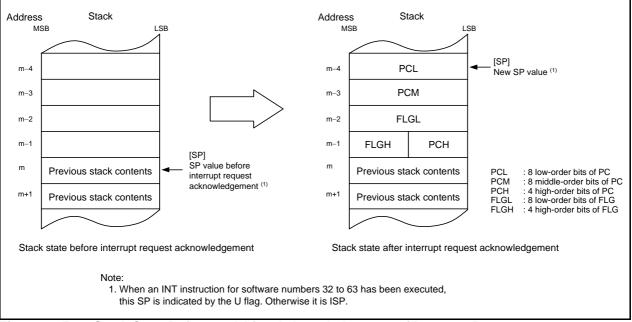

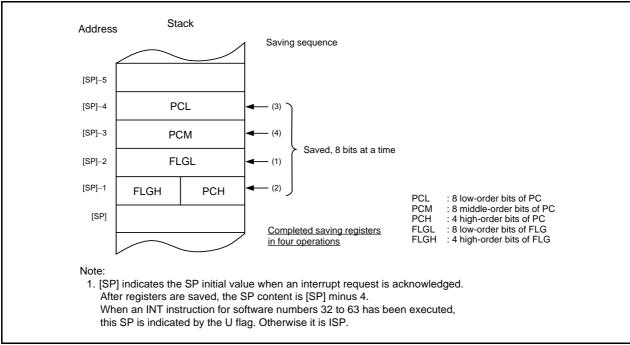

| 12.3.  | 7 Saving Registers                                                                                                                                                                       | 179   |

| 12.3.  | 8 Returning from Interrupt Routine                                                                                                                                                       | 181   |

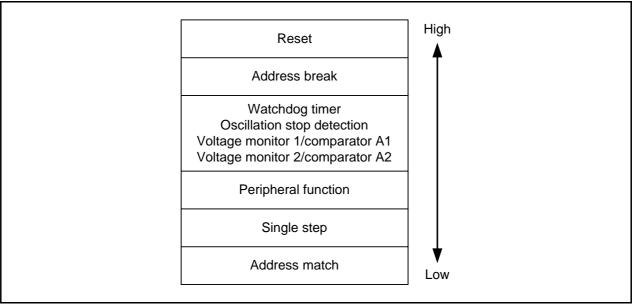

| 12.3.  | 9 Interrupt Priority                                                                                                                                                                     | 181   |

| 12.3.  | 10 Interrupt Priority Level Selection Circuit                                                                                                                                            | 182   |

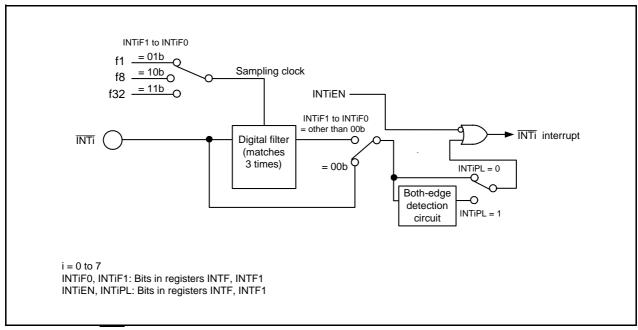

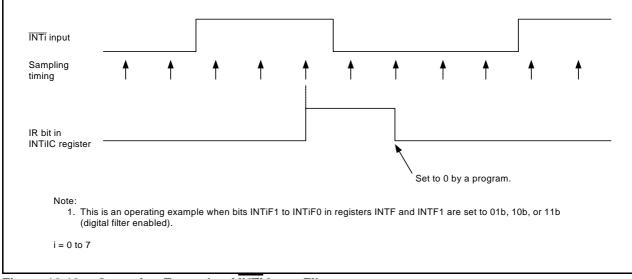

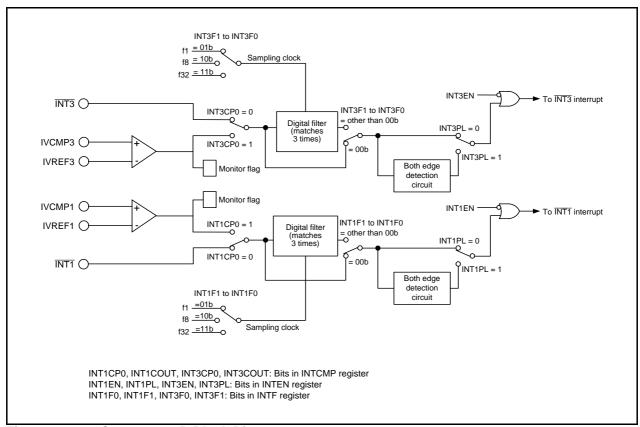

| 12.4   | INT Interrupt                                                                                                                                                                            | 183   |

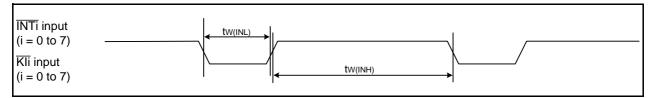

| 12.4.  | 1 $\overline{\text{INTi}}$ Interrupt (i = 0 to 7)                                                                                                                                        | 183   |

| 12.4.  |                                                                                                                                                                                          |       |

| 12.4.  | 3 External Input Enable Register 0 (INTEN)                                                                                                                                               | 185   |

| 12.4.  | 4 External Input Enable Register 1 (INTEN1)                                                                                                                                              | 186   |

| 12.4.  | 5 INT Input Filter Select Register 0 (INTF)                                                                                                                                              | 187   |

| 12.4.  | 6 INT Input Filter Select Register 1 (INTF1)                                                                                                                                             | 187   |

| 12.4.  |                                                                                                                                                                                          |       |

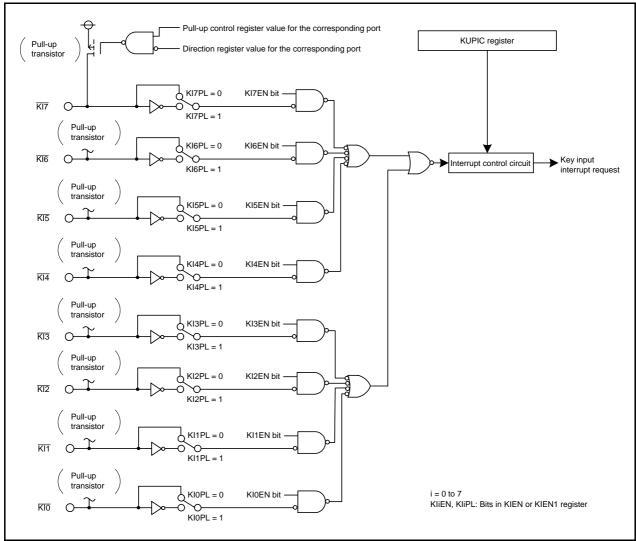

| 12.5   | Key Input Interrupt                                                                                                                                                                      |       |

| 12.5.  | 1 Key Input Pin Select Register (KISR)                                                                                                                                                   | 191   |

| 12.5.  | 2 Key Input Enable Register 0 (KIEN)                                                                                                                                                     | 192   |

| 12.5.  |                                                                                                                                                                                          |       |

| 12.6   | Address Match Interrupt                                                                                                                                                                  | 194   |

| 12.6.  | •                                                                                                                                                                                        |       |

| 12.6.  |                                                                                                                                                                                          |       |

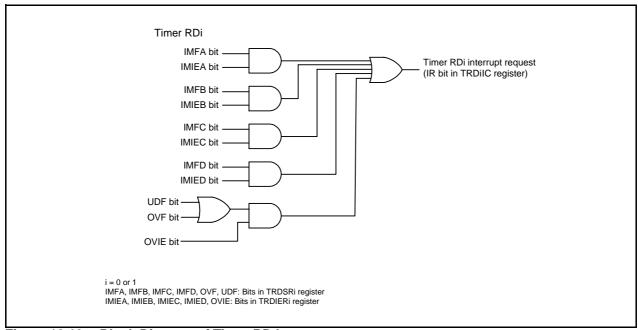

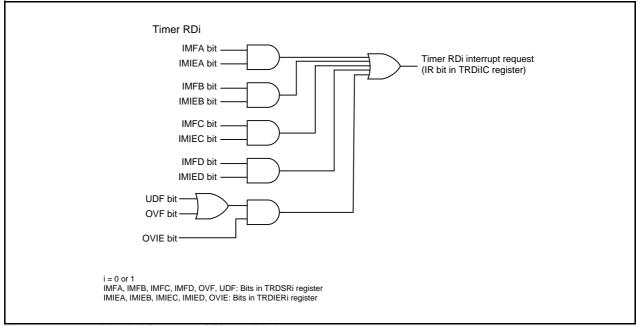

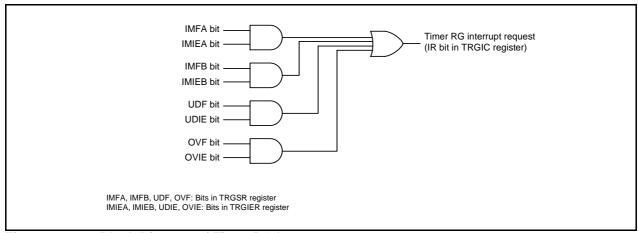

| 12.7   | Interrupts of Timer RC, Timer RD, Timer RG, Synchronous Serial Communication Unit, I <sup>2</sup> C bus Interface, and Flash Memory (Interrupts with Multiple Interrupt Request Sources) |       |

| 12.8   | Notes on Interrupts                                                                                                                                                                      |       |

|        | 1                                                                                                                                                                                        |       |

| 12.8.1  | Reading Address 00000h                                      | 198 |

|---------|-------------------------------------------------------------|-----|

| 12.8.2  | SP Setting                                                  | 198 |

| 12.8.3  | External Interrupt, Key Input Interrupt                     | 198 |

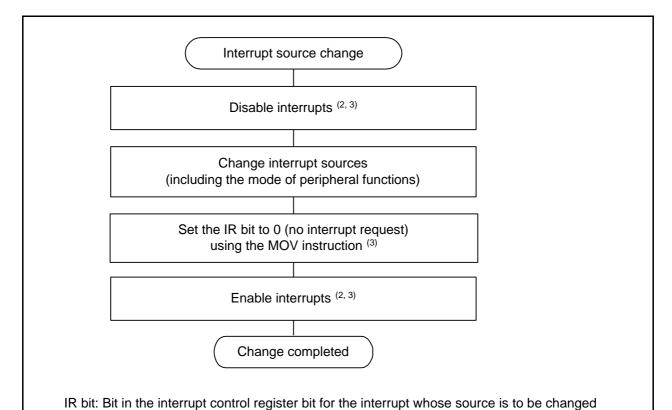

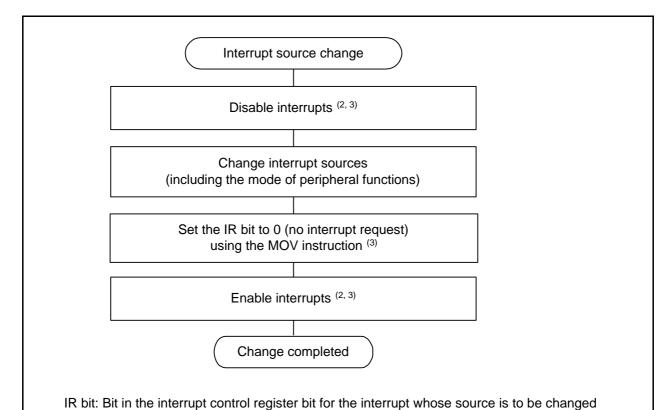

| 12.8.4  | Changing Interrupt Sources                                  | 199 |

| 12.8.5  | Rewriting Interrupt Control Register                        | 200 |

| 40 ID ( | Nada Assas                                                  | 204 |

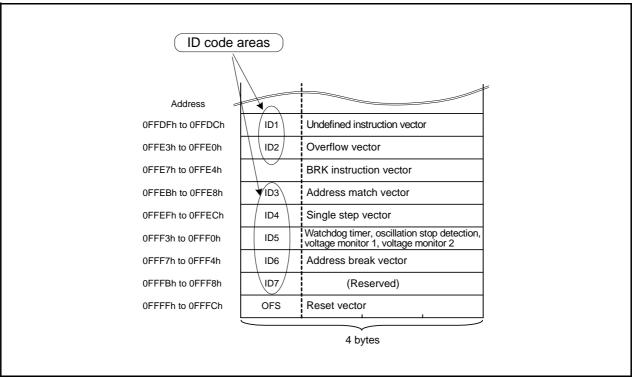

|         | Code Areas                                                  |     |

|         | Introduction                                                |     |

|         | Functions                                                   |     |

|         | Forced Erase Function                                       |     |

|         |                                                             |     |

|         | Notes on ID Code Areas                                      |     |

| 13.5.1  | Setting Example of ID Code Areas                            | 204 |

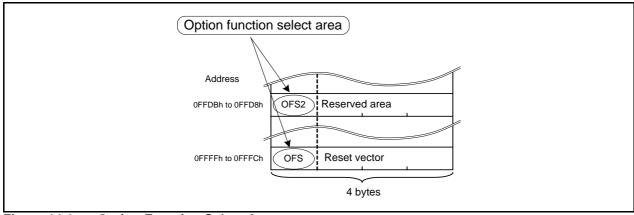

| 14. Opt | on Function Select Area                                     | 205 |

| 14.1    | Introduction                                                | 205 |

| 14.2    | Registers                                                   | 206 |

| 14.2.1  | Option Function Select Register (OFS)                       | 206 |

| 14.2.2  | Option Function Select Register 2 (OFS2)                    | 207 |

| 14.3    | Notes on Option Function Select Area                        | 208 |

| 14.3.1  | Setting Example of Option Function Select Area              | 208 |

| 45 \\/_ | alada a Timan                                               | 000 |

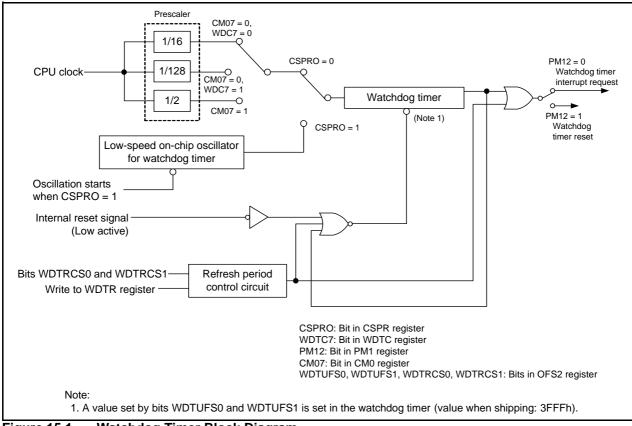

|         | chdog Timer                                                 |     |

|         | Introduction                                                |     |

|         | Registers                                                   |     |

| 15.2.1  | Processor Mode Register 1 (PM1)                             |     |

| 15.2.2  | Watchdog Timer Reset Register (WDTR)                        |     |

| 15.2.3  | Watchdog Timer Start Register (WDTS)                        |     |

| 15.2.4  | Watchdog Timer Control Register (WDTC)                      |     |

| 15.2.5  | Count Source Protection Mode Register (CSPR)                |     |

| 15.2.6  | Option Function Select Register (OFS)                       |     |

| 15.2.7  | Option Function Select Register 2 (OFS2)                    |     |

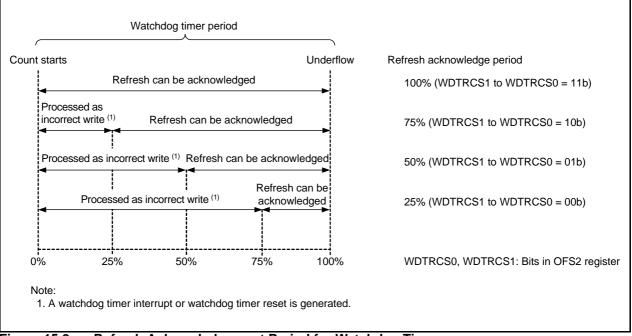

| 15.3    | Functional Description                                      |     |

| 15.3.1  | Common Items for Multiple Modes                             |     |

| 15.3.2  | Count Source Protection Mode Disabled                       |     |

| 15.3.3  | Count Source Protection Mode Enabled                        | 217 |

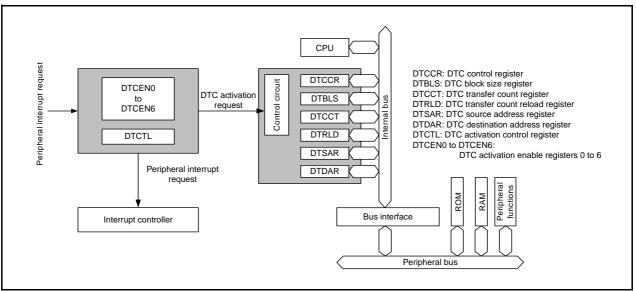

| 16. DTC | >                                                           | 218 |

| 16.1    | Overview                                                    | 218 |

| 16.2    | Registers                                                   | 219 |

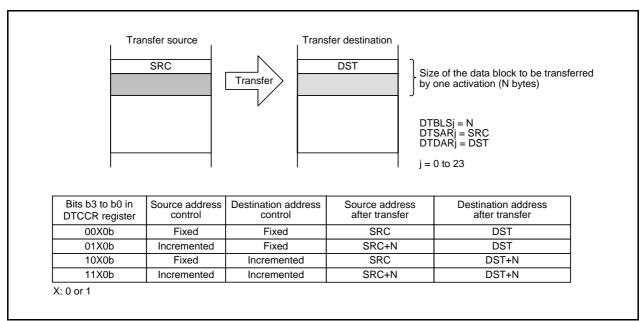

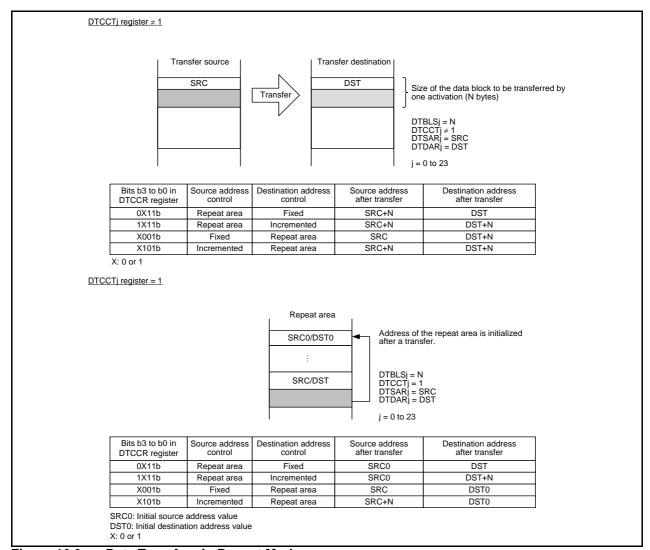

| 16.2.1  | DTC Control Register j (DTCCRj) (j = 0 to 23)               | 220 |

| 16.2.2  | DTC Block Size Register j (DTBLSj) (j = 0 to 23)            | 220 |

| 16.2.3  | DTC Transfer Count Register j (DTCCTj) (j = 0 to 23)        | 221 |

| 16.2.4  | DTC Transfer Count Reload Register j (DTRLDj) (j = 0 to 23) |     |

| 16.2.5  | DTC Source Address Register j (DTSARj) (j = 0 to 23)        |     |

| 16.2.6  | DTC Destination Address Register j (DTDARj) (j = 0 to 23)   |     |

| 16.2.7  | DTC Activation Enable Register i (DTCENi) (i = 0 to 6)      |     |

| 16.2.8  | DTC Activation Control Register (DTCTL)                     |     |

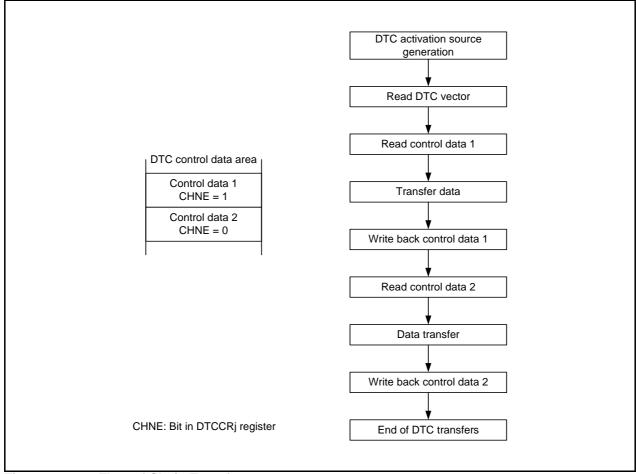

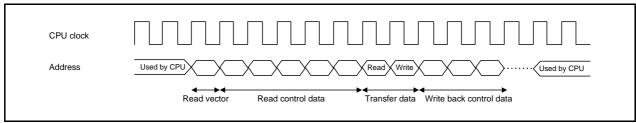

|         | Function Description                                        | 224 |

| 16.3.1   | Overview                                                                | 224  |

|----------|-------------------------------------------------------------------------|------|

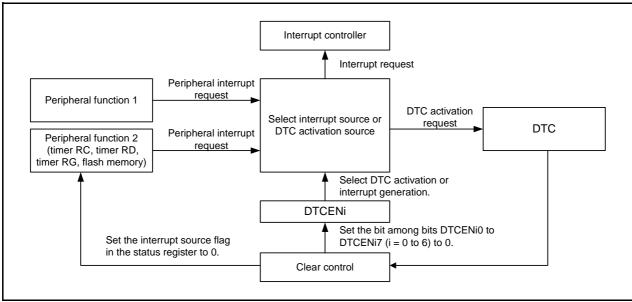

| 16.3.2   | Activation Sources                                                      | 224  |

| 16.3.3   | Control Data Allocation and DTC Vector Table                            | 226  |

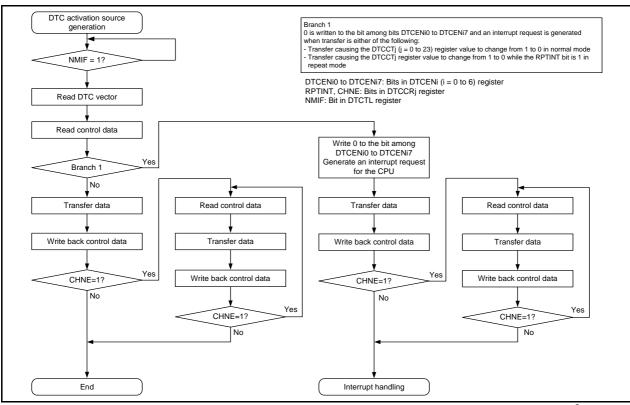

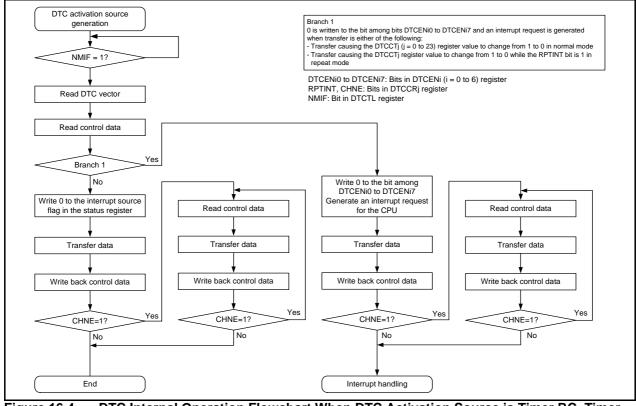

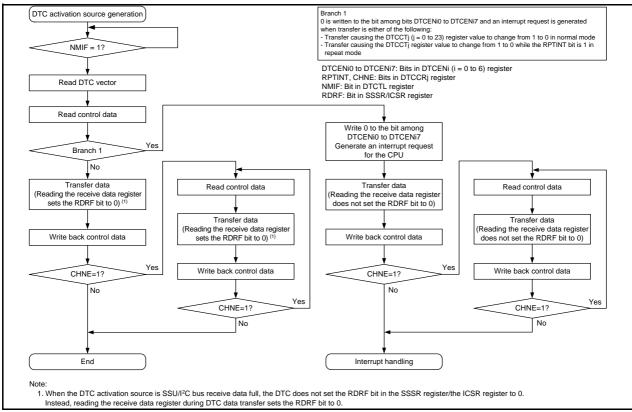

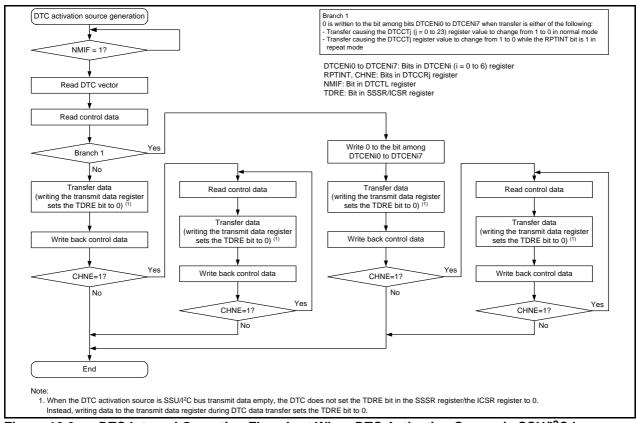

| 16.3.4   | Normal Mode                                                             | 231  |

| 16.3.5   | Repeat Mode                                                             | 232  |

| 16.3.6   | Chain Transfers                                                         | 233  |

| 16.3.7   | Interrupt Sources                                                       | 233  |

| 16.3.8   | Operation Timings                                                       | 234  |

| 16.3.9   | Number of DTC Execution Cycles                                          | 235  |

| 16.3.10  | DTC Activation Source Acknowledgement and Interrupt Source Flags        | 236  |

| 16.4     | Notes on DTC                                                            | 237  |

| 16.4.1   | DTC activation source                                                   | 237  |

| 16.4.2   | DTCENi (i = 0 to 6) Registers                                           | 237  |

| 16.4.3   | Peripheral Modules                                                      | 237  |

| 16.4.4   | Interrupt Request                                                       | 237  |

| 17. Time | ers                                                                     | 238  |

| 18. Time | er RA                                                                   | 240  |

| 18.1     | Introduction                                                            | 240  |

| 18.2 I   | Registers                                                               | 241  |

| 18.2.1   | Timer RA Control Register (TRACR)                                       | 241  |

| 18.2.2   | Timer RA I/O Control Register (TRAIOC)                                  | 241  |

| 18.2.3   | Timer RA Mode Register (TRAMR)                                          | 242  |

| 18.2.4   | Timer RA Prescaler Register (TRAPRE)                                    | 242  |

| 18.2.5   | Timer RA Register (TRA)                                                 |      |

| 18.2.6   | Timer RA Pin Select Register (TRASR)                                    |      |

| 18.3     | Timer Mode                                                              |      |

| 18.3.1   | Timer RA I/O Control Register (TRAIOC) in Timer Mode                    |      |

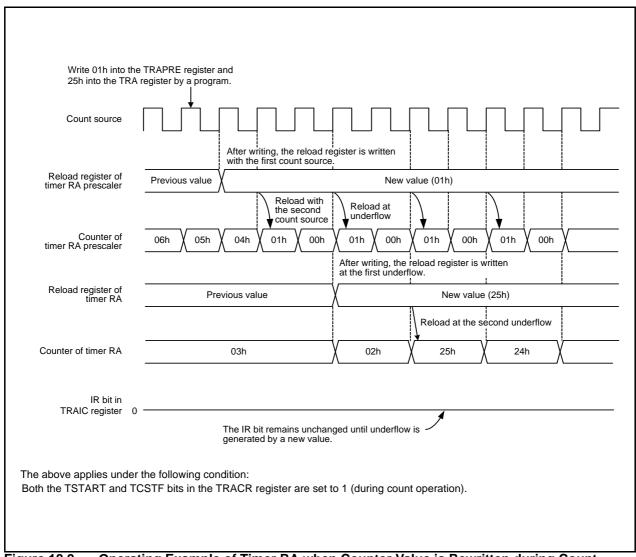

| 18.3.2   | Timer Write Control during Count Operation                              |      |

|          | Pulse Output Mode                                                       |      |

| 18.4.1   | Timer RA I/O Control Register (TRAIOC) in Pulse Output Mode             |      |

|          | Event Counter Mode                                                      |      |

| 18.5.1   | Timer RA I/O Control Register (TRAIOC) in Event Counter Mode            |      |

|          | Pulse Width Measurement Mode                                            |      |

| 18.6.1   | Timer RA I/O Control Register (TRAIOC) in Pulse Width Measurement Mode  |      |

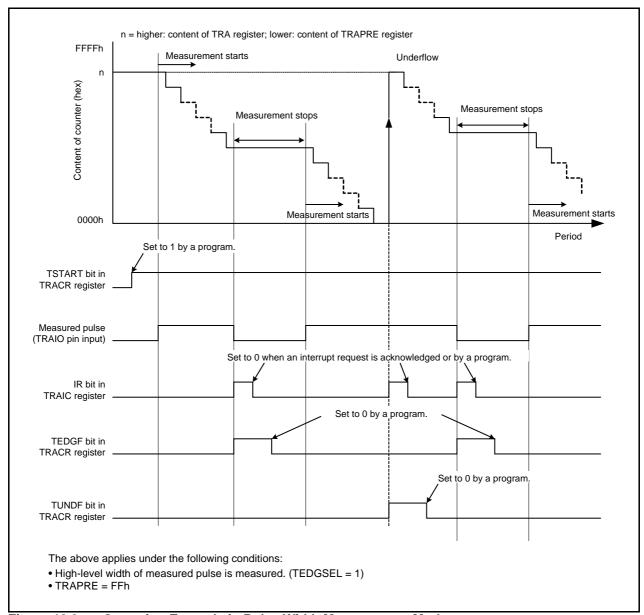

| 18.6.2   | Operating Example                                                       |      |

|          | Pulse Period Measurement Mode                                           |      |

| 18.7.1   | Timer RA I/O Control Register (TRAIOC) in Pulse Period Measurement Mode |      |

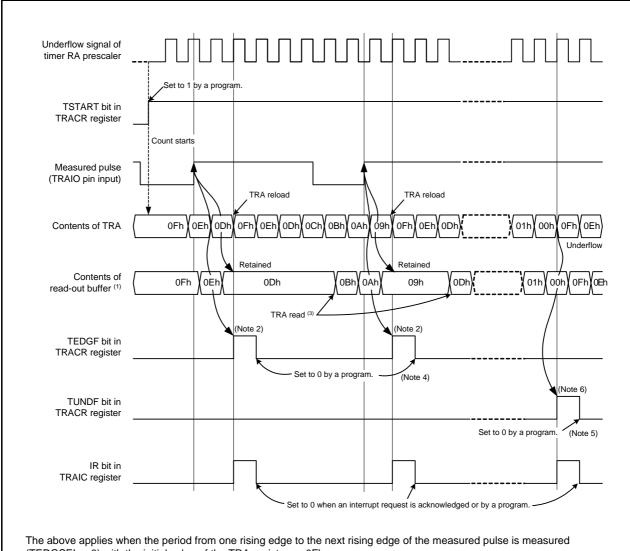

| 18.7.2   | Operating Example                                                       |      |

|          | Notes on Timer RA                                                       |      |

| 19. Time | er RB                                                                   | 257  |

|          | Introduction                                                            |      |

|          | Registers                                                               |      |

| 19.2.1   | Timer RB Control Register (TRBCR)                                       |      |

| 19.2.1   | Timer RB One-Shot Control Register (TRBOCR)                             |      |

| 19.2.2   |                                                                         |      |

| 19.2.3   | Timer RB I/O Control Register (TRBIOC)                                  |      |

| 17.4.4   | THICLIND MOUE REVINELLINDMIN.                                           | 4.19 |

| 19.2.5   | Timer RB Prescaler Register (TRBPRE)                                                 | 260   |

|----------|--------------------------------------------------------------------------------------|-------|

| 19.2.6   | Timer RB Secondary Register (TRBSC)                                                  | 260   |

| 19.2.7   | Timer RB Primary Register (TRBPR)                                                    | 261   |

| 19.2.8   | Timer RB/RC Pin Select Register (TRBRCSR)                                            | 261   |

| 19.3 Т   | Cimer Mode                                                                           | 262   |

| 19.3.1   | Timer RB I/O Control Register (TRBIOC) in Timer Mode                                 | 262   |

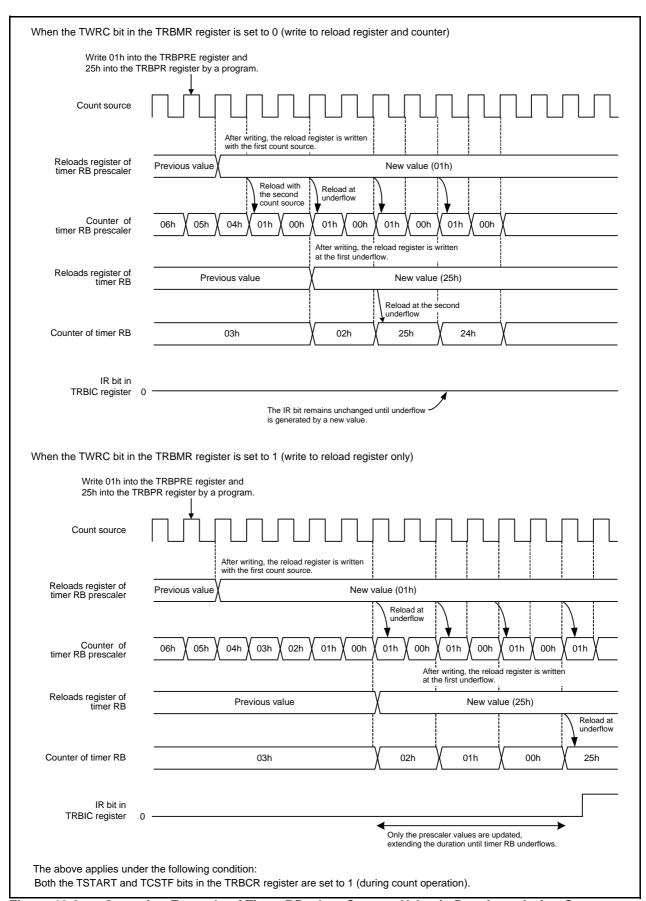

| 19.3.2   | Timer Write Control during Count Operation                                           | 263   |

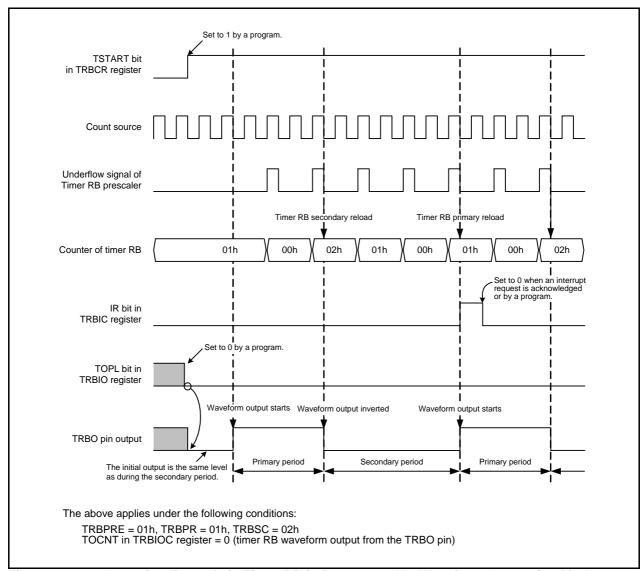

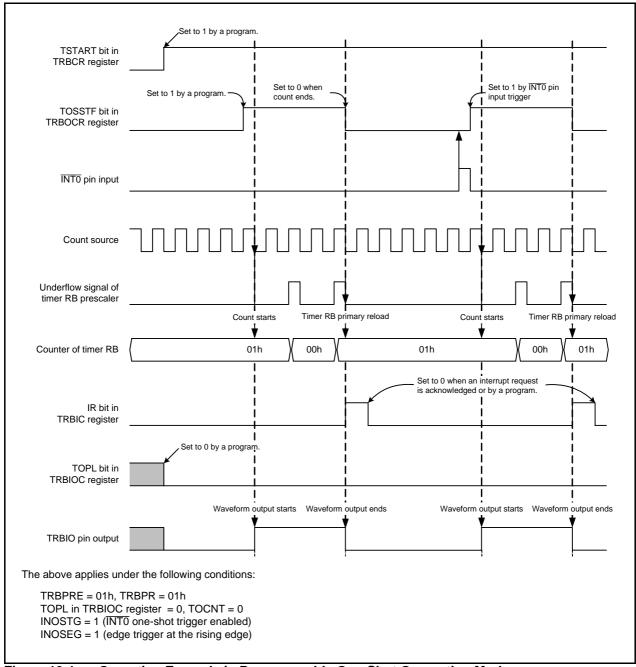

| 19.4 F   | Programmable Waveform Generation Mode                                                |       |

| 19.4.1   | Timer RB I/O Control Register (TRBIOC) in Programmable Waveform Generation Mode      | 266   |

| 19.4.2   | Operating Example                                                                    |       |

| 19.5 F   | Programmable One-shot Generation Mode                                                |       |

| 19.5.1   | Timer RB I/O Control Register (TRBIOC) in Programmable One-Shot Generation Mode      |       |

| 19.5.2   | Operating Example                                                                    |       |

| 19.5.3   | One-Shot Trigger Selection                                                           |       |

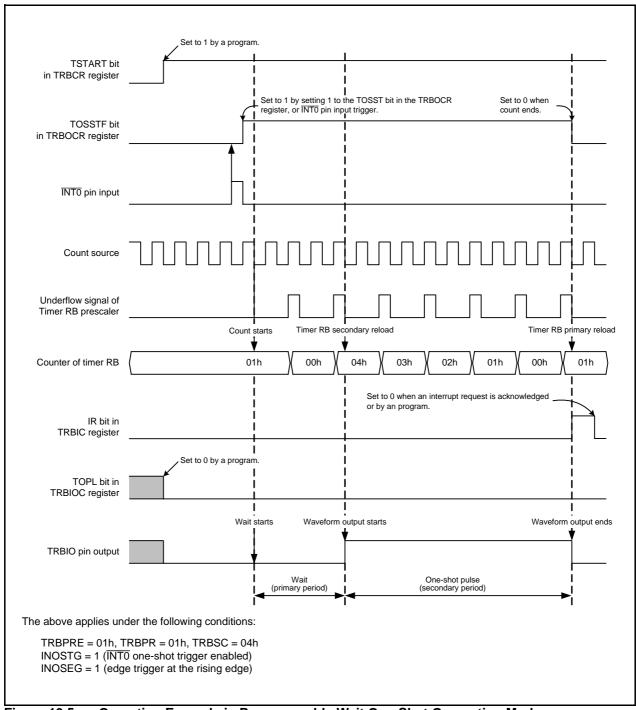

|          | Programmable Wait One-Shot Generation Mode                                           |       |

| 19.6.1   | Timer RB I/O Control Register (TRBIOC) in Programmable Wait One-Shot Generation Mode |       |

| 19.6.2   | Operating Example                                                                    |       |

|          | Notes on Timer RB                                                                    |       |

| 19.7.1   | Timer Mode                                                                           |       |

| 19.7.2   | Programmable Waveform Generation Mode                                                |       |

| 19.7.3   | Programmable One-Shot Generation Mode                                                |       |

| 19.7.4   | Programmable Wait One-shot Generation Mode                                           |       |

|          | .6                                                                                   |       |

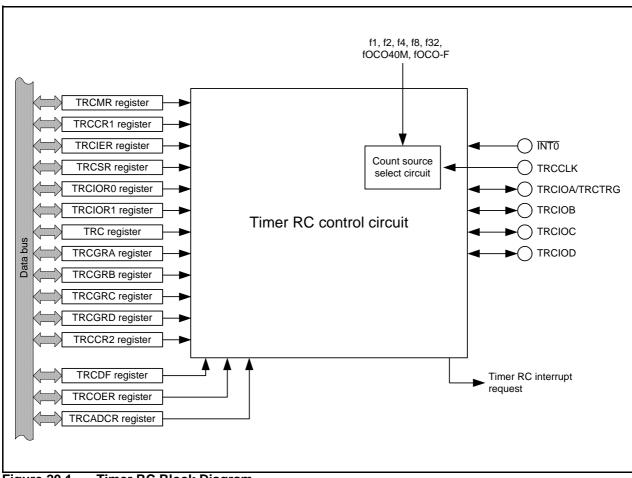

| 20. Time | r RC                                                                                 | . 277 |

| 20.1 I   | ntroduction                                                                          | 277   |

|          | Registers                                                                            |       |

| 20.2.1   | Module Standby Control Register (MSTCR)                                              |       |

| 20.2.2   | Timer RC Mode Register (TRCMR)                                                       |       |

| 20.2.3   | Timer RC Control Register 1 (TRCCR1)                                                 |       |

| 20.2.4   | Timer RC Interrupt Enable Register (TRCIER)                                          |       |

| 20.2.5   | Timer RC Status Register (TRCSR)                                                     |       |

| 20.2.6   | Timer RC I/O Control Register 0 (TRCIOR0)                                            |       |

| 20.2.7   | Timer RC I/O Control Register 1 (TRCIOR1)                                            |       |

| 20.2.8   | Timer RC Counter (TRC)                                                               |       |

| 20.2.9   | Timer RC General Registers A, B, C, and D (TRCGRA, TRCGRB, TRCGRC, TRCGRD)           |       |

| 20.2.10  | Timer RC Control Register 2 (TRCCR2)                                                 |       |

| 20.2.11  | Timer RC Digital Filter Function Select Register (TRCDF)                             |       |

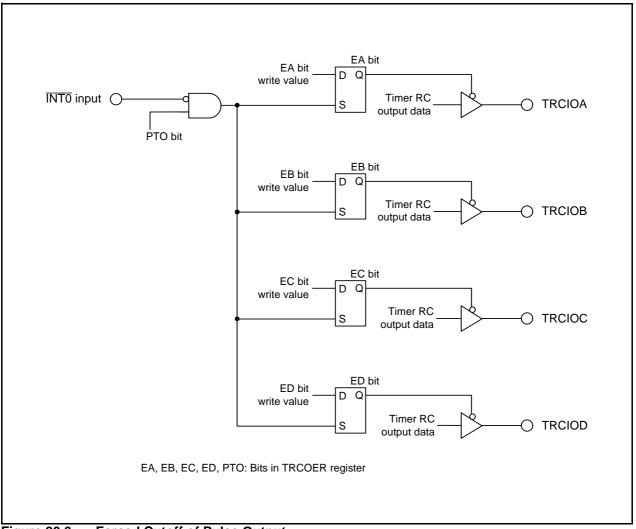

| 20.2.12  | Timer RC Output Master Enable Register (TRCOER)                                      |       |

| 20.2.13  | Timer RC Trigger Control Register (TRCADCR)                                          |       |

| 20.2.14  | Timer RB/RC Pin Select Register (TRBRCSR)                                            |       |

| 20.2.15  | Timer RC Pin Select Register 0 (TRCPSR0)                                             |       |

| 20.2.16  | Timer RC Pin Select Register 1 (TRCPSR1)                                             |       |

|          | Common Items for Multiple Modes                                                      |       |

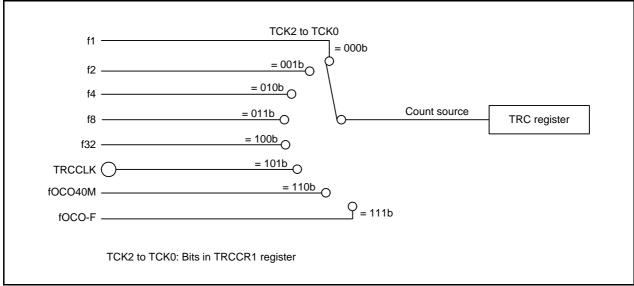

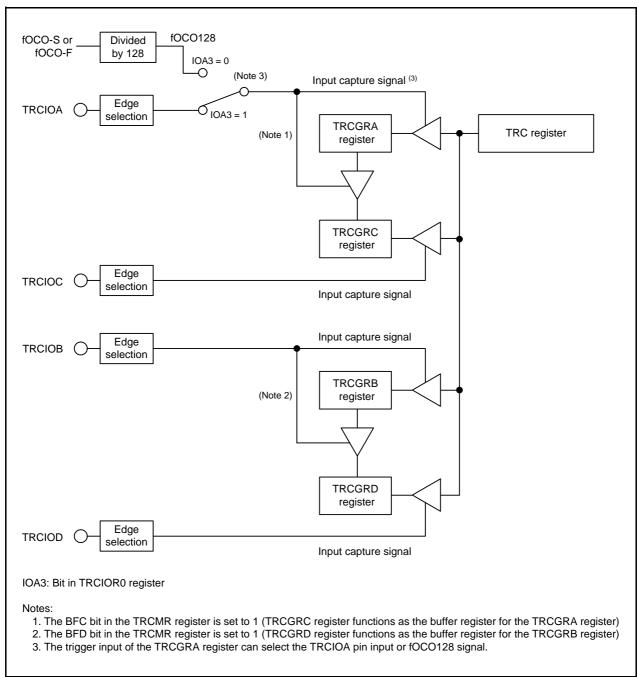

| 20.3.1   | Count Source                                                                         |       |

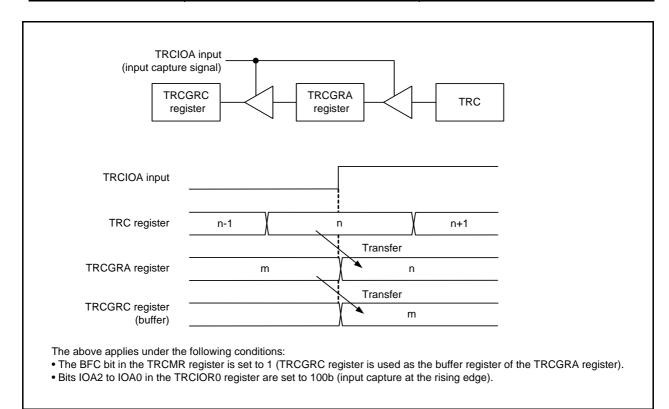

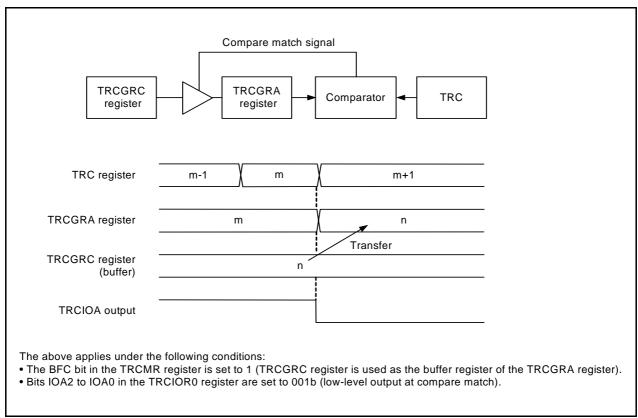

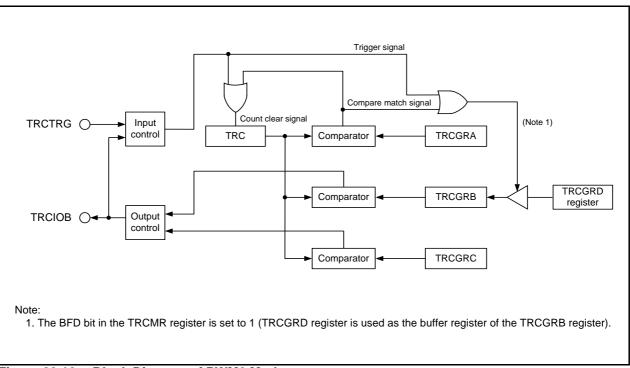

| 20.3.1   | Buffer Operation                                                                     |       |

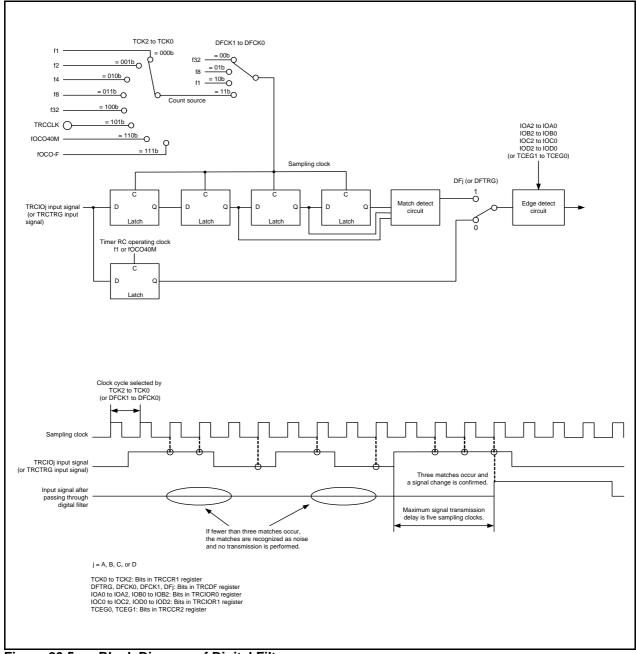

| 20.3.2   | Digital Filter                                                                       |       |

| 20.3.4   | Forced Cutoff of Pulse Output                                                        |       |

|          | Fimer Mode (Input Capture Function)                                                  |       |

| 20.4.1   | Timer RC I/O Control Register 0 (TRCIOR0) in Timer Mode (Input Capture Function)     |       |

|          |                                                                                      |       |

| 20.4.2  | Timer RC I/O Control Register 1 (TRCIOR1) in Timer Mode (Input Capture Function)          | 301 |

|---------|-------------------------------------------------------------------------------------------|-----|

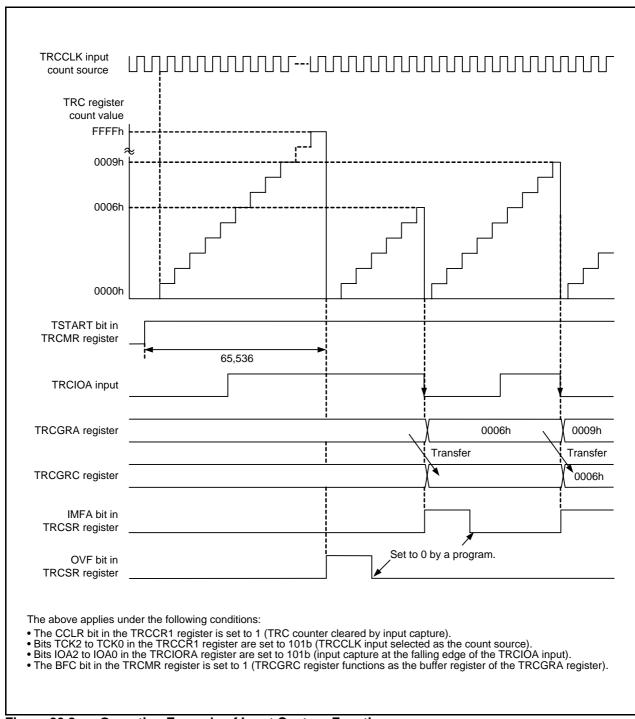

| 20.4.3  | Operating Example                                                                         | 302 |

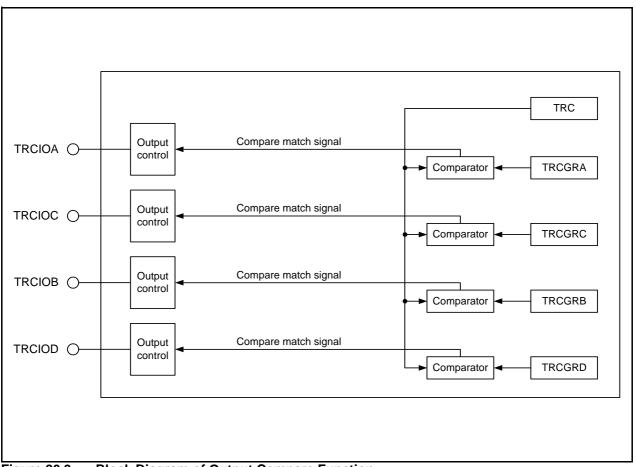

| 20.5    | Timer Mode (Output Compare Function)                                                      | 303 |

| 20.5.1  | Timer RC Control Register 1 (TRCCR1) in Timer Mode (Output Compare Function)              | 305 |

| 20.5.2  | Timer RC I/O Control Register 0 (TRCIOR0) in Timer Mode (Output Compare Function)         | 306 |

| 20.5.3  | Timer RC I/O Control Register 1 (TRCIOR1) in Timer Mode (Output Compare Function)         | 307 |

| 20.5.4  | Timer RC Control Register 2 (TRCCR2) in Timer Mode (Output Compare Function)              | 308 |

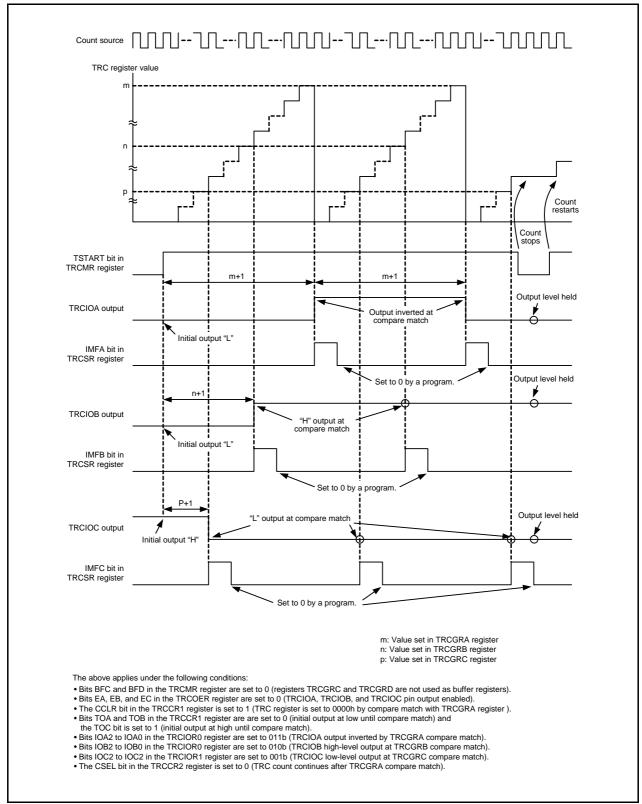

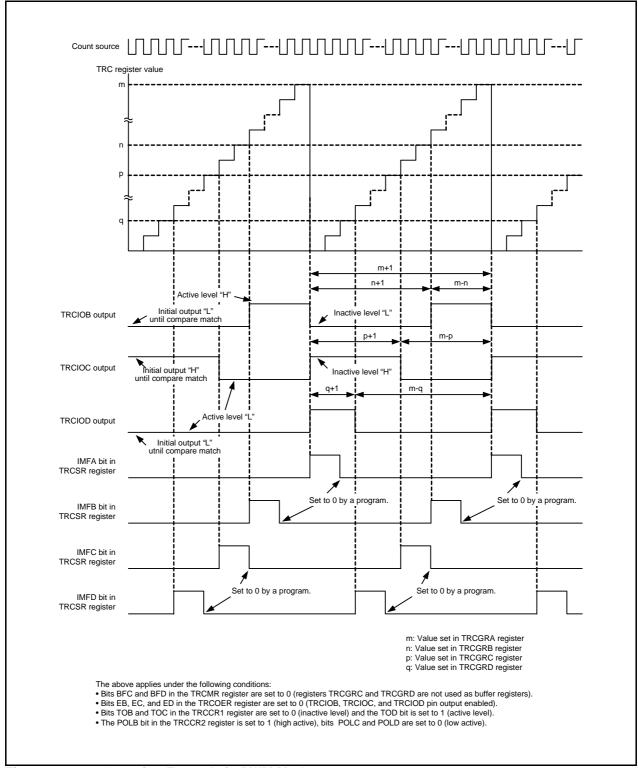

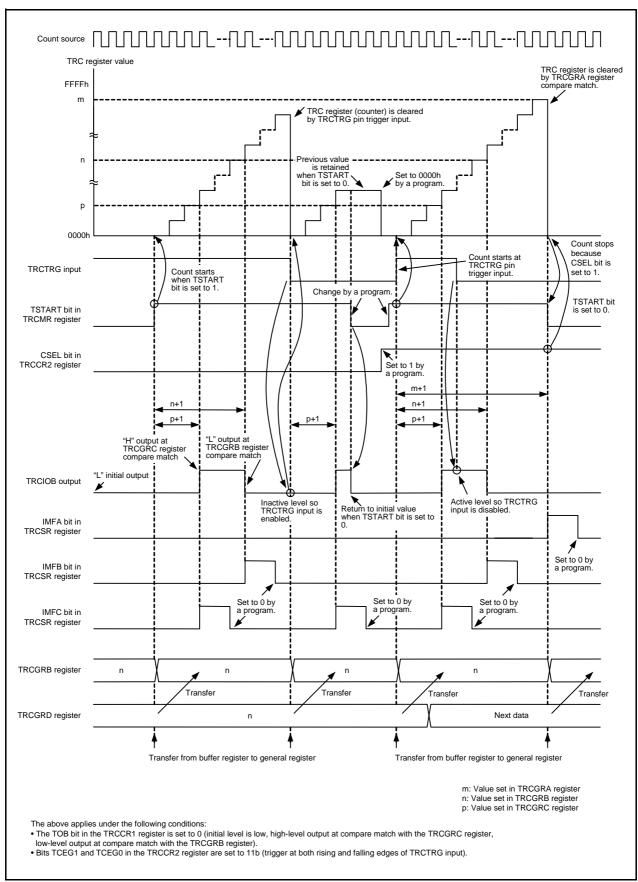

| 20.5.5  | Operating Example                                                                         | 309 |

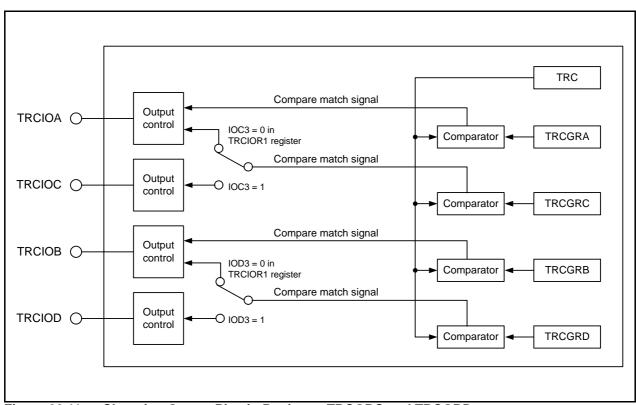

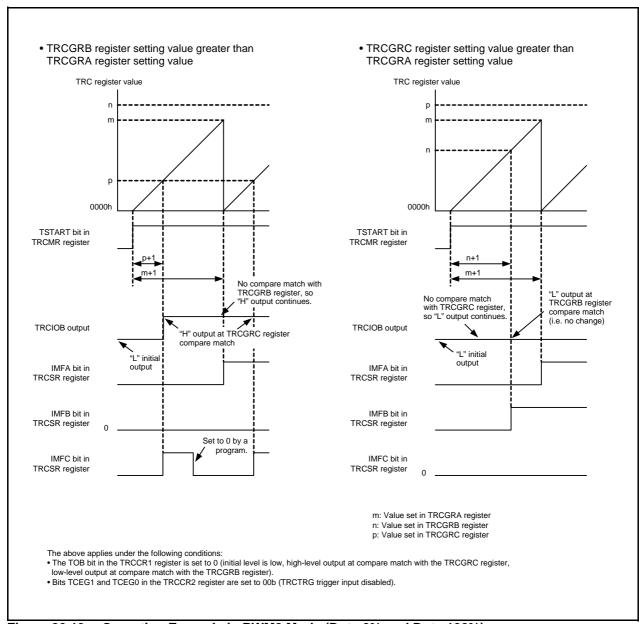

| 20.5.6  | Changing Output Pins in Registers TRCGRC and TRCGRD                                       | 310 |

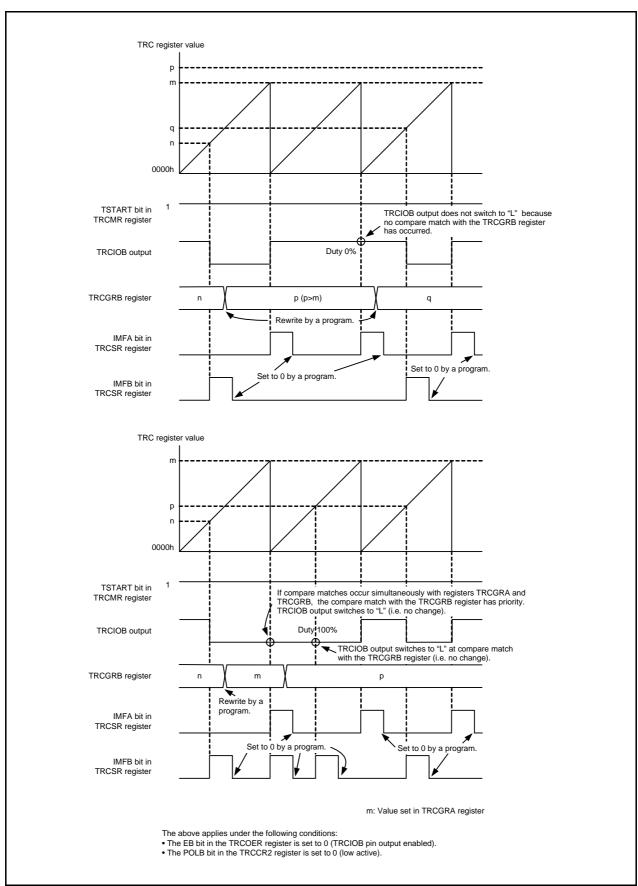

| 20.6    | PWM Mode                                                                                  | 312 |

| 20.6.1  | Timer RC Control Register 1 (TRCCR1) in PWM Mode                                          | 314 |

| 20.6.2  | Timer RC Control Register 2 (TRCCR2) in PWM Mode                                          | 315 |

| 20.6.3  | Operating Example                                                                         | 316 |

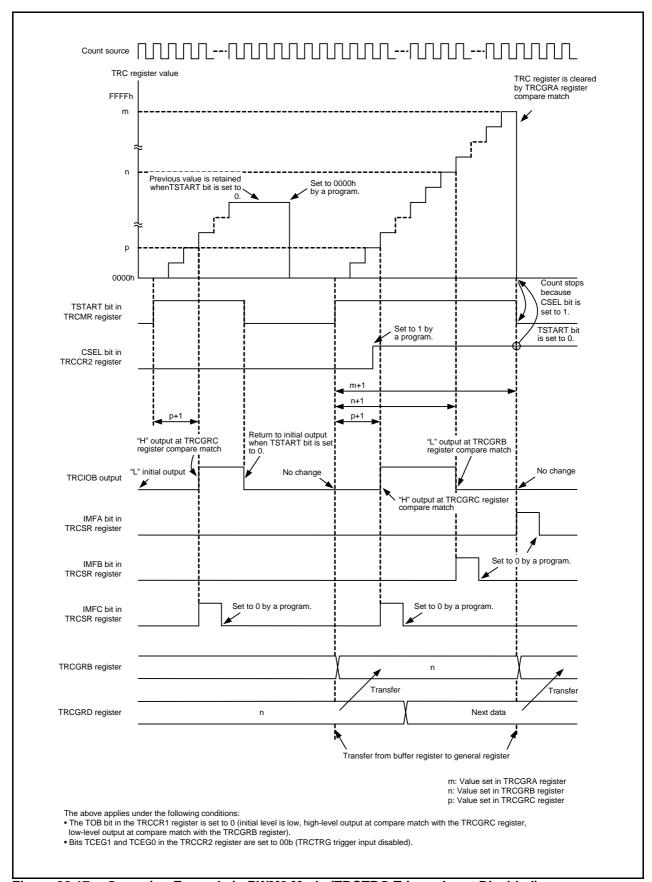

| 20.7    | PWM2 Mode                                                                                 | 318 |

| 20.7.1  | Timer RC Control Register 1 (TRCCR1) in PWM2 Mode                                         | 320 |

| 20.7.2  | Timer RC Control Register 2 (TRCCR2) in PWM2 Mode                                         | 321 |

| 20.7.3  | Timer RC Digital Filter Function Select Register (TRCDF) in PWM2 Mode                     | 322 |

| 20.7.4  | Operating Example                                                                         | 323 |

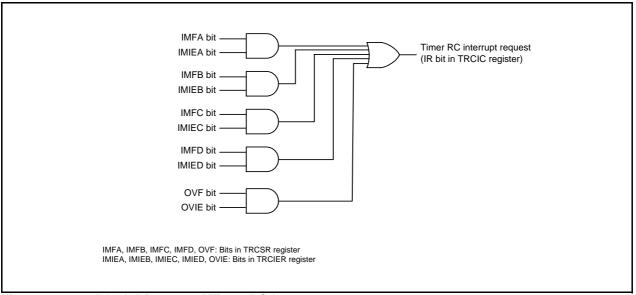

| 20.8    | Timer RC Interrupt                                                                        | 326 |

| 20.9    | Notes on Timer RC                                                                         | 327 |

| 20.9.1  | TRC Register                                                                              | 327 |

| 20.9.2  | TRCSR Register                                                                            | 327 |

| 20.9.3  | TRCCR1 Register                                                                           | 327 |

| 20.9.4  | Count Source Switching                                                                    | 327 |

| 20.9.5  | Input Capture Function                                                                    | 328 |

| 20.9.6  | TRCMR Register in PWM2 Mode                                                               | 328 |

| 20.9.7  | Count Source fOCO40M                                                                      | 328 |

|         |                                                                                           |     |

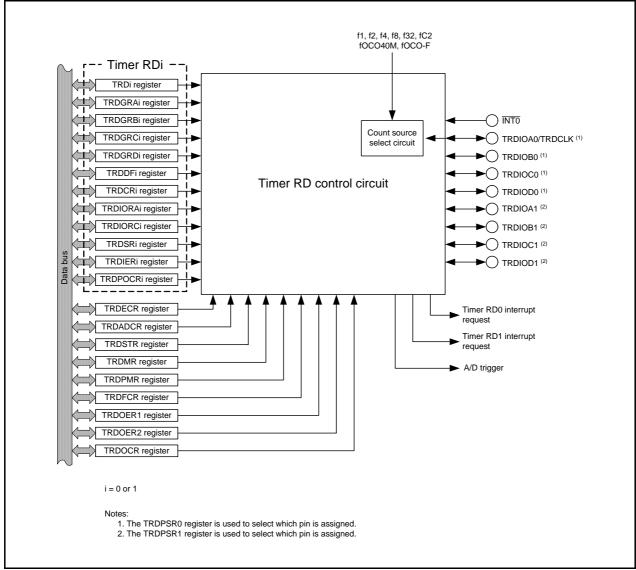

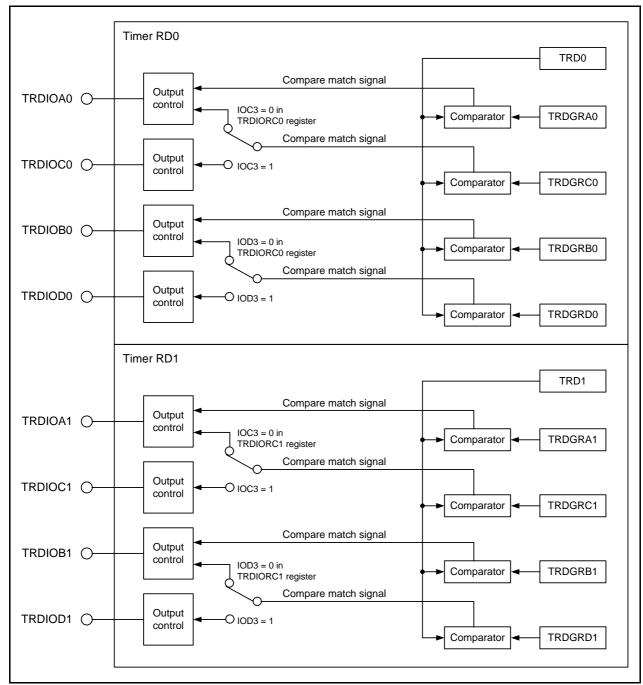

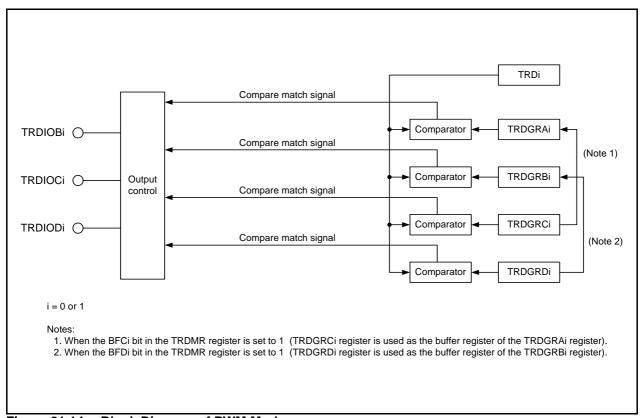

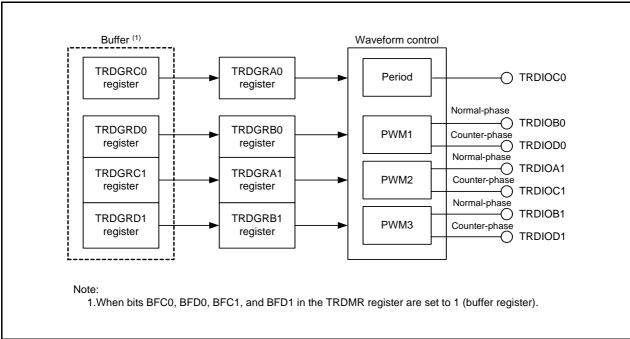

| 21. Tim | er RD                                                                                     |     |

| 21.1    | Introduction                                                                              | 329 |

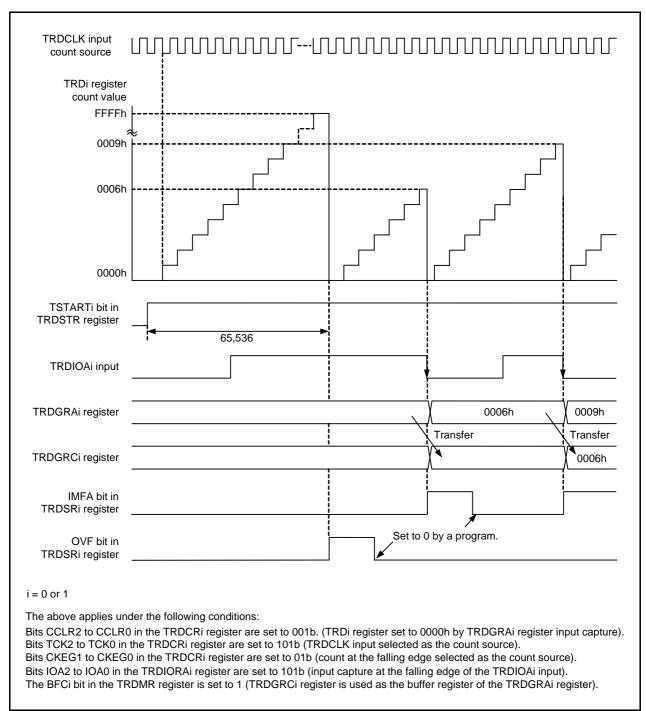

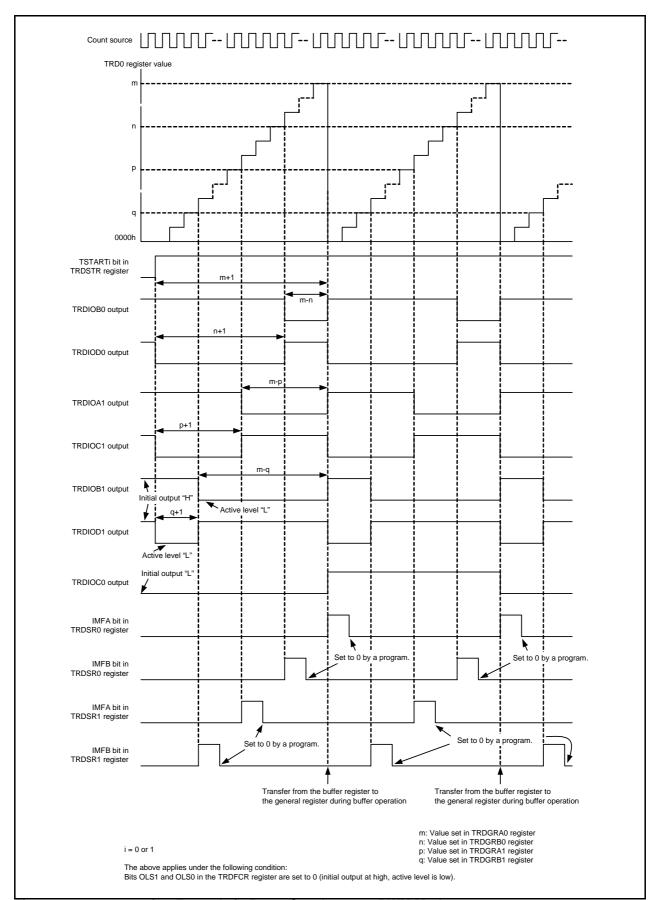

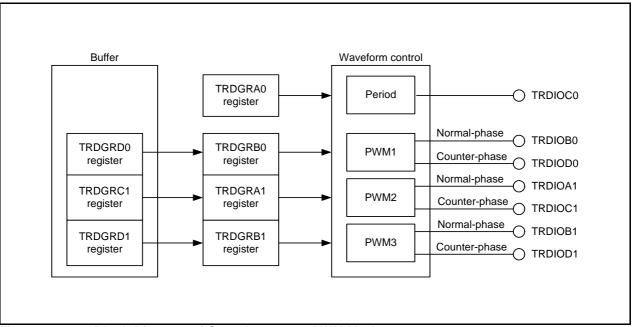

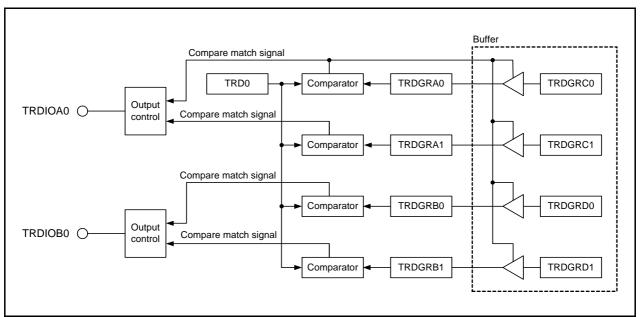

| 21.2    | Common Items for Multiple Modes                                                           | 331 |

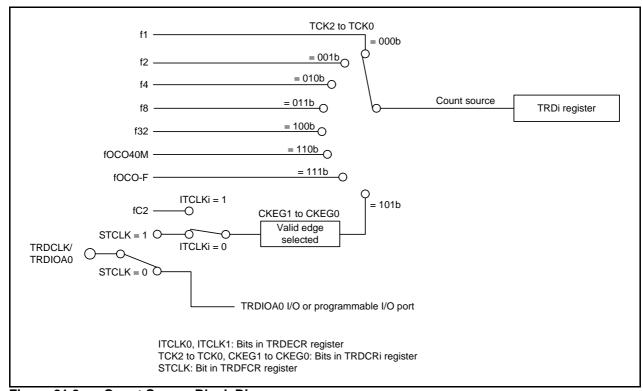

| 21.2.1  | Count Sources                                                                             | 331 |

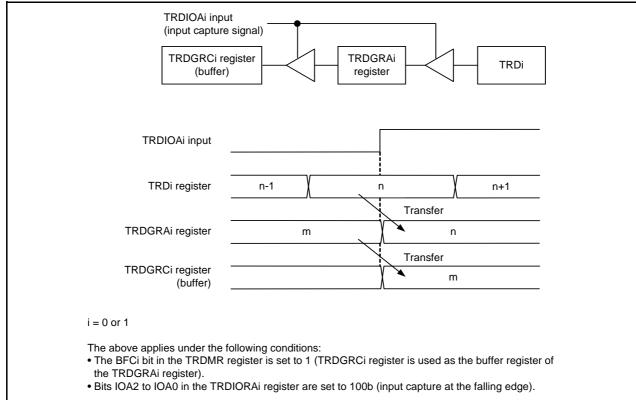

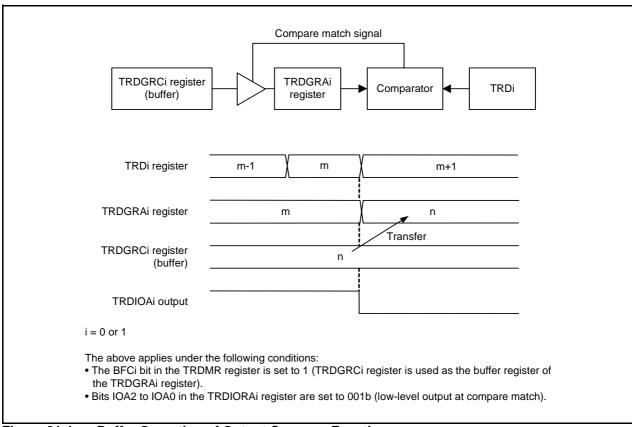

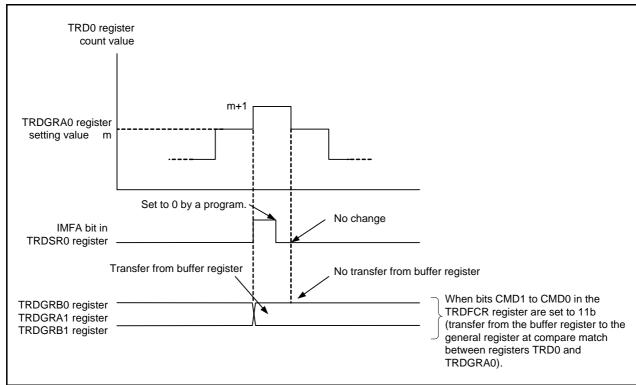

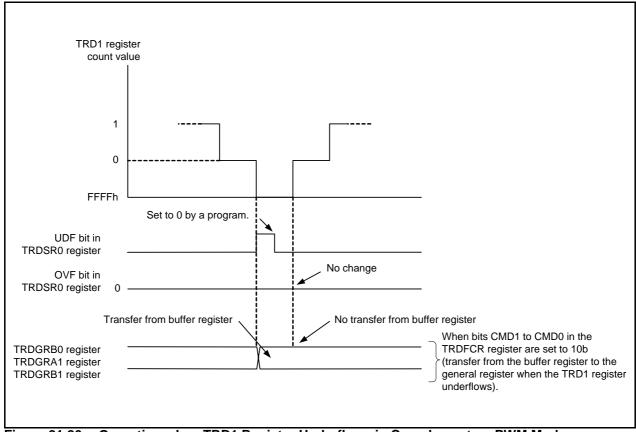

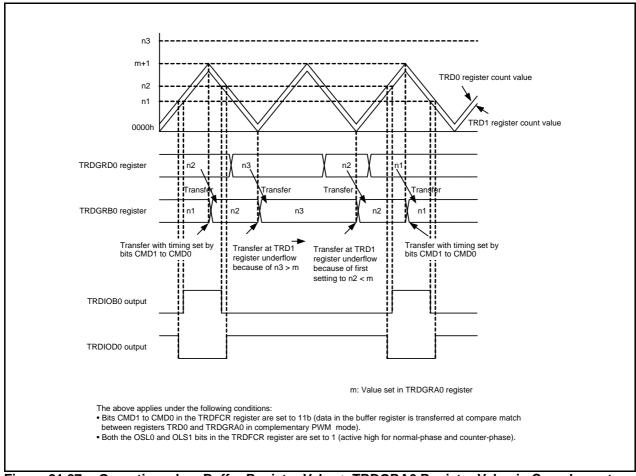

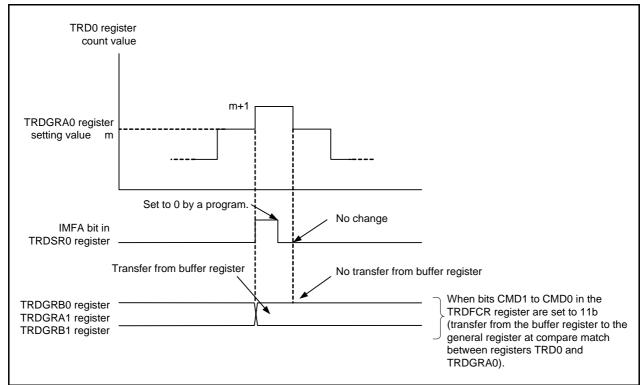

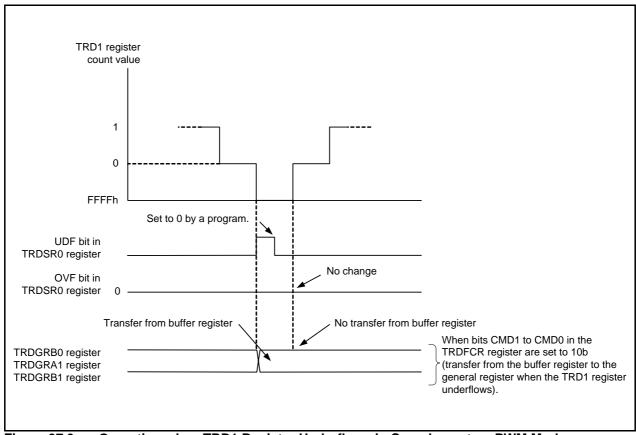

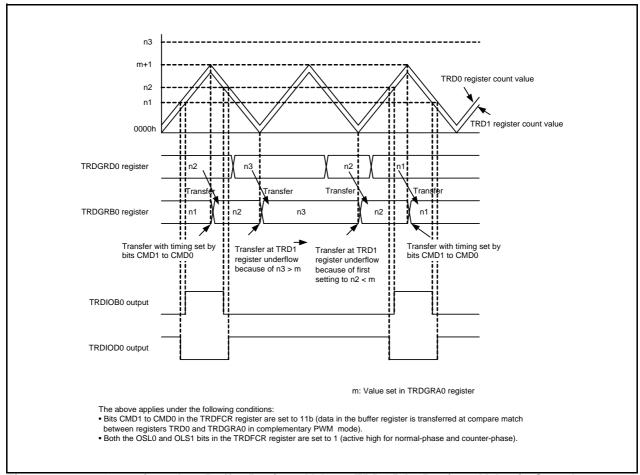

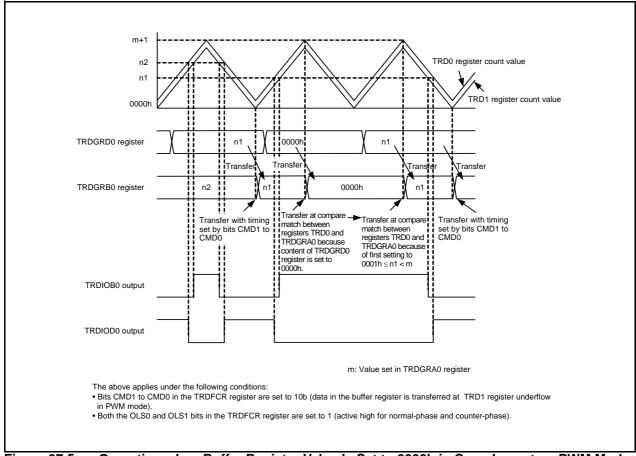

| 21.2.2  | Buffer Operation                                                                          | 332 |

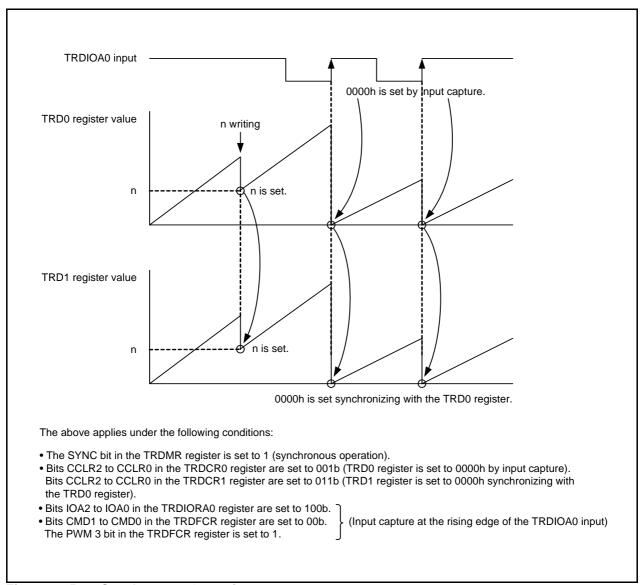

| 21.2.3  | Synchronous Operation                                                                     |     |

| 21.2.4  | Pulse Output Forced Cutoff                                                                | 335 |

| 21.3    | Input Capture Function                                                                    |     |

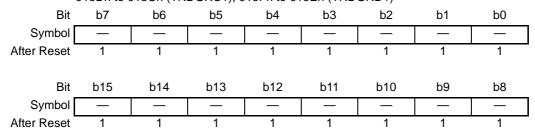

| 21.3.1  | Module Standby Control Register (MSTCR)                                                   |     |

| 21.3.2  | Timer RD Control Expansion Register (TRDECR)                                              | 339 |

| 21.3.3  | Timer RD Start Register (TRDSTR) for Input Capture Function                               | 340 |

| 21.3.4  | Timer RD Mode Register (TRDMR) for Input Capture Function                                 | 340 |

| 21.3.5  | Timer RD PWM Mode Register (TRDPMR) for Input Capture Function                            | 341 |

| 21.3.6  | Timer RD Function Control Register (TRDFCR) for Input Capture Function                    | 341 |

| 21.3.7  | Timer RD Digital Filter Function Select Register i (TRDDFi) ( $i = 0$ or 1)               |     |

|         | for Input Capture Function                                                                |     |

| 21.3.8  | Timer RD Control Register i (TRDCRi) (i = 0 or 1) for Input Capture Function              |     |

| 21.3.9  | Timer RD I/O Control Register Ai (TRDIORAi) (i = 0 or 1) for Input Capture Function       |     |

| 21.3.10 |                                                                                           |     |

| 21.3.1  |                                                                                           |     |

| 21 3 1  | Timer RD Interrupt Enable Register i (TRDIFRi) $(i - 0)$ or 1) for Input Capture Function | 347 |

| 21.3.13 | Timer RD Counter i (TRDi) ( $i = 0$ or 1) for Input Capture Function                                                      | 347 |

|---------|---------------------------------------------------------------------------------------------------------------------------|-----|

| 21.3.14 | Timer RD General Registers Ai, Bi, Ci, and Di (TRDGRAi, TRDGRBi, TRDGRCi, TRDGRDi)                                        |     |

|         | (i = 0 or 1) for Input Capture Function                                                                                   |     |

| 21.3.15 | Timer RD Pin Select Register 0 (TRDPSR0)                                                                                  |     |

| 21.3.16 | Timer RD Pin Select Register 1 (TRDPSR1)                                                                                  |     |

| 21.3.17 | Operating Example                                                                                                         |     |

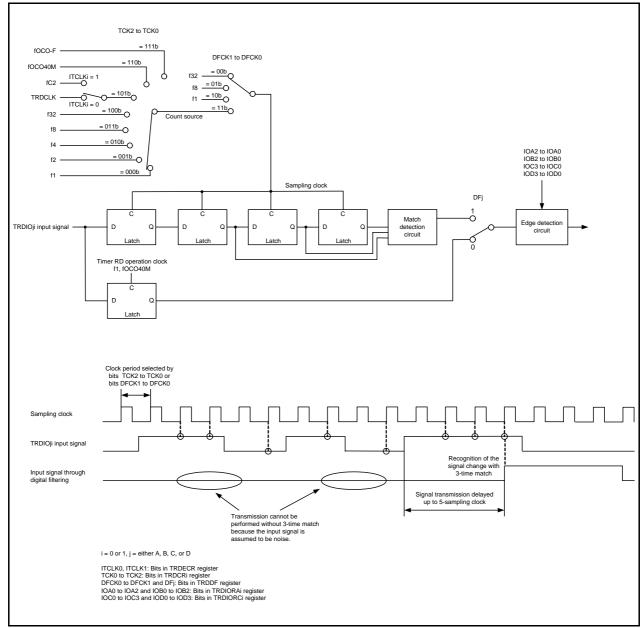

| 21.3.18 | Digital Filter                                                                                                            |     |

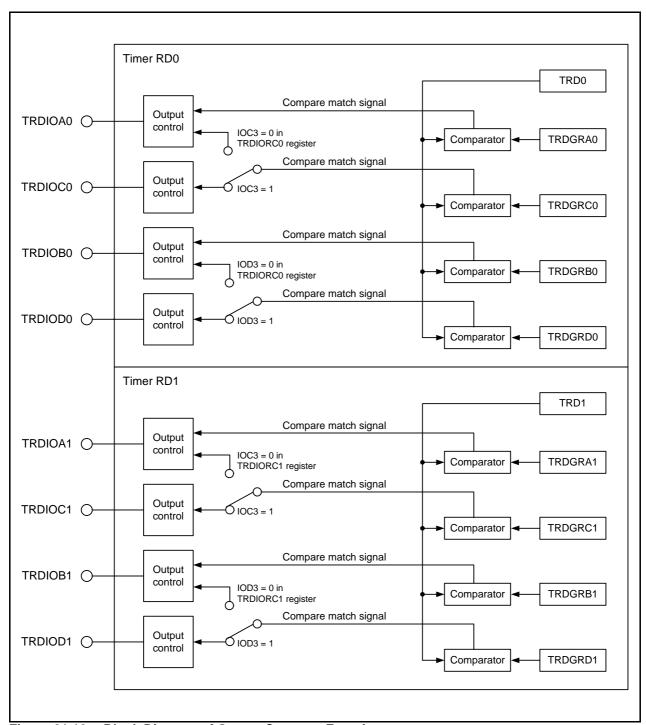

|         | utput Compare Function                                                                                                    |     |

| 21.4.1  | Module Standby Control Register (MSTCR)                                                                                   |     |

| 21.4.2  | Timer RD Control Expansion Register (TRDECR)                                                                              |     |

| 21.4.3  | Timer RD Trigger Control Register (TRDADCR)                                                                               |     |

| 21.4.4  | Timer RD Start Register (TRDSTR) for Output Compare Function                                                              |     |

| 21.4.5  | Timer RD Mode Register (TRDMR) for Output Compare Function                                                                |     |

| 21.4.6  | Timer RD PWM Mode Register (TRDPMR) for Output Compare Function                                                           |     |

| 21.4.7  | Timer RD Function Control Register (TRDFCR) for Output Compare Function                                                   |     |

| 21.4.8  | Timer RD Output Master Enable Register 1 (TRDOER1) for Output Compare Function                                            |     |

| 21.4.9  | Timer RD Output Master Enable Register 2 (TRDOER2) for Output Compare Function                                            |     |

| 21.4.10 | Timer RD Output Control Register (TRDOCR) for Output Compare Function                                                     |     |

| 21.4.11 | Timer RD Control Register i (TRDCRi) (i = 0 or 1) for Output Compare Function                                             |     |

| 21.4.12 | $\label{eq:control} \mbox{Timer RD I/O Control Register Ai (TRDIORAi) (i = 0 \mbox{ or } 1) for Output Compare Function}$ |     |

| 21.4.13 | Timer RD I/O Control Register Ci (TRDIORCi) (i = 0 or 1) for Output Compare Function                                      |     |

| 21.4.14 | Timer RD Status Register i (TRDSRi) (i = 0 or 1) for Output Compare Function                                              |     |

| 21.4.15 | Timer RD Interrupt Enable Register i (TRDIERi) ( $i = 0$ or 1) for Output Compare Function                                |     |

| 21.4.16 | Timer RD Counter i (TRDi) ( $i = 0$ or 1) for Output Compare Function                                                     | 366 |

| 21.4.17 | Timer RD General Registers Ai, Bi, Ci, and Di (TRDGRAi, TRDGRBi, TRDGRCi, TRDGRDi)                                        | 267 |

| 21 1 10 | (i = 0 or 1) for Output Compare Function                                                                                  |     |

| 21.4.18 | Timer RD Pin Select Register 0 (TRDPSR0)                                                                                  |     |

| 21.4.19 | Timer RD Pin Select Register 1 (TRDPSR1)                                                                                  |     |

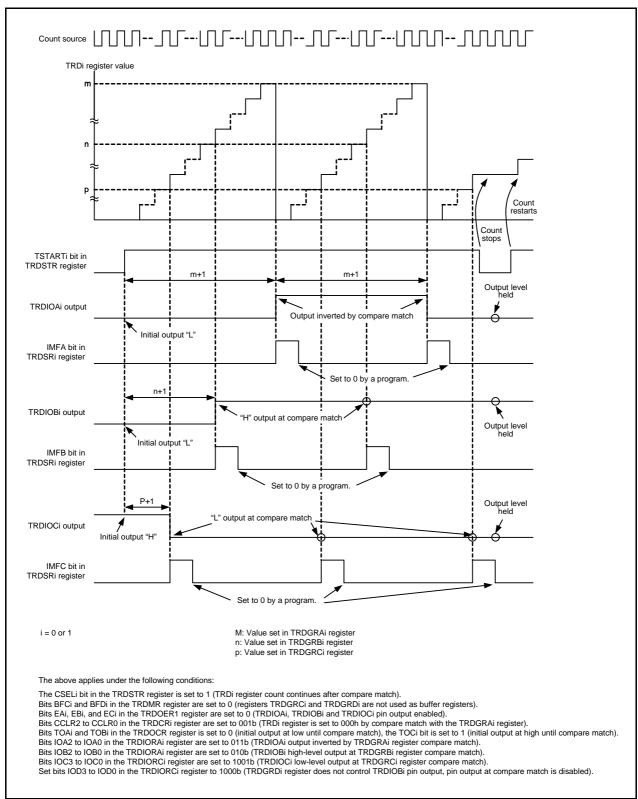

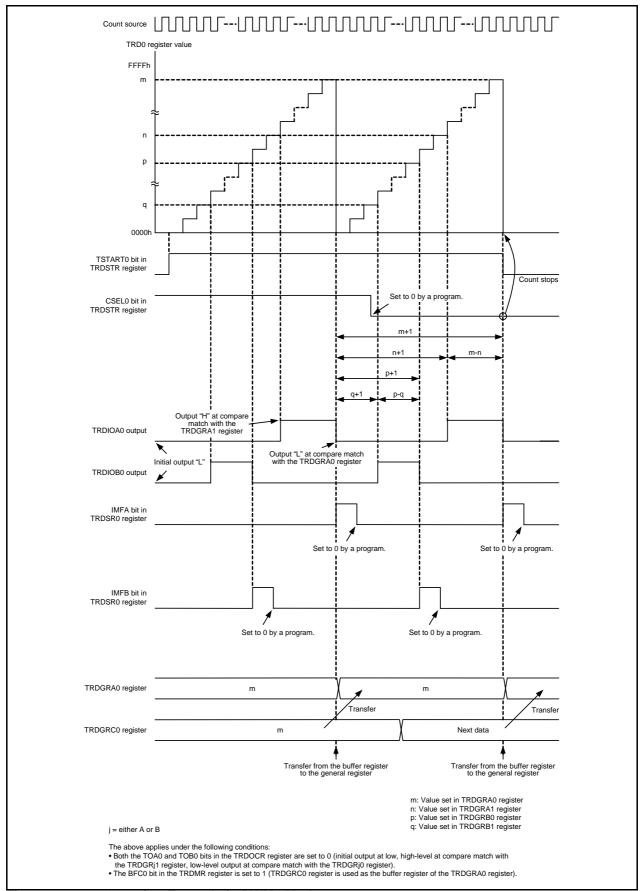

| 21.4.20 | Operating Example                                                                                                         |     |

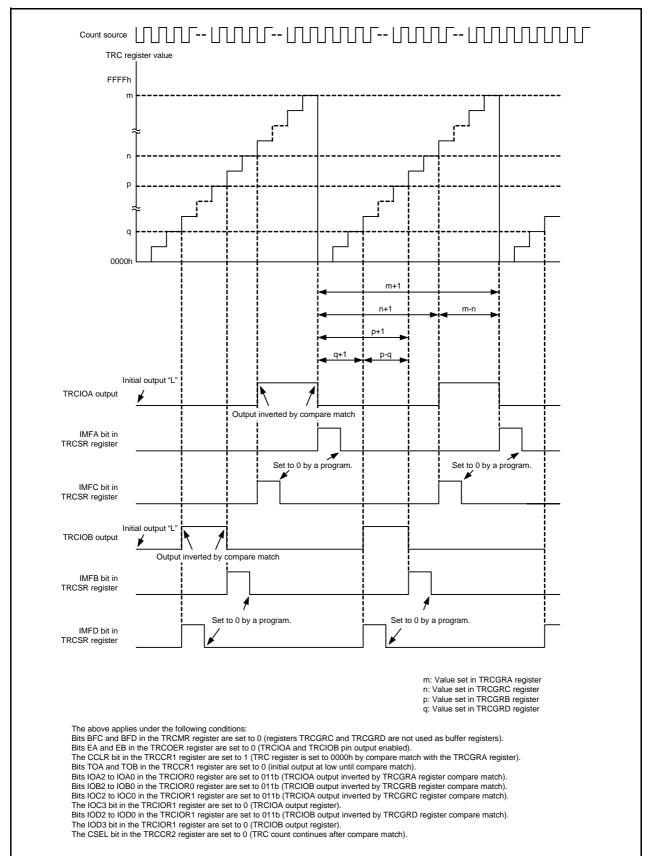

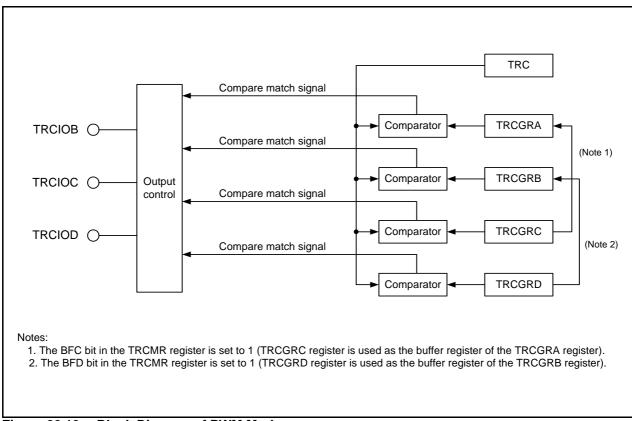

| 21.4.21 | Changing Output Pins in Registers TRDGRCi (i = 0 or 1) and TRDGRDi                                                        |     |

| 21.4.22 | A/D Trigger Generation                                                                                                    |     |

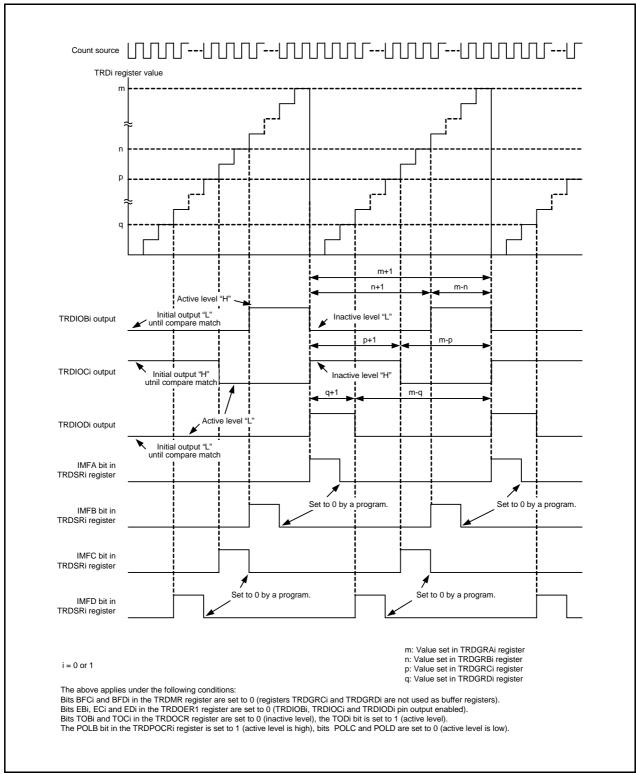

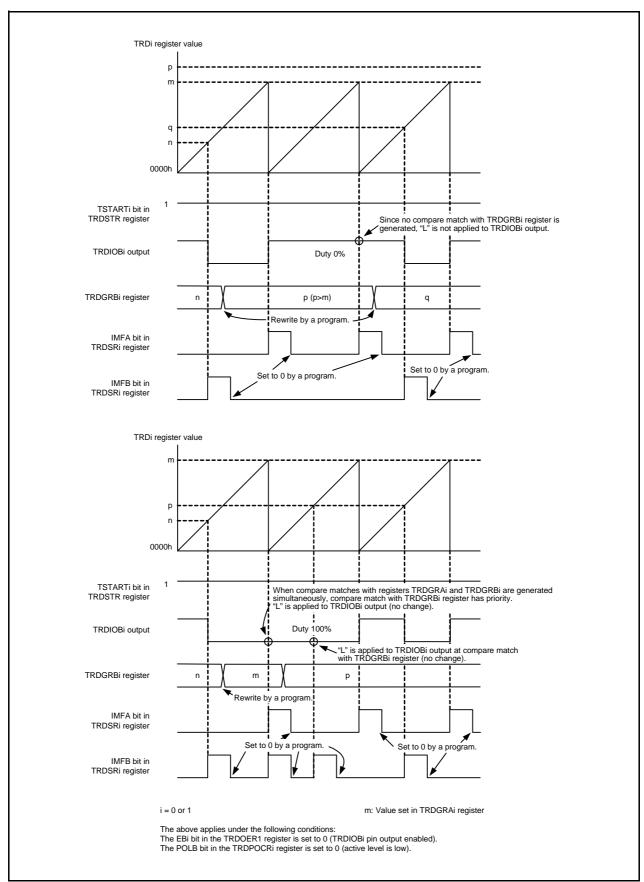

|         | WM Mode                                                                                                                   |     |

|         | Module Standby Control Register (MSTCR)                                                                                   |     |

| 21.5.2  | Timer RD Control Expansion Register (TRDECR)                                                                              |     |

| 21.5.3  | Timer RD Trigger Control Register (TRDADCR)                                                                               |     |

| 21.5.4  | Timer RD Start Register (TRDSTR) in PWM Mode                                                                              |     |

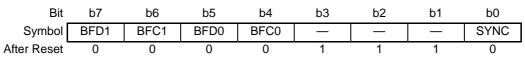

| 21.5.5  | Timer RD Mode Register (TRDMR) in PWM Mode                                                                                |     |

| 21.5.6  | Timer RD PWM Mode Register (TRDPMR) in PWM Mode                                                                           |     |

| 21.5.7  | Timer RD Function Control Register (TRDFCR) in PWM Mode                                                                   |     |

| 21.5.8  | Timer RD Output Master Enable Register 1 (TRDOER1) in PWM Mode                                                            |     |

| 21.5.9  | Timer RD Output Master Enable Register 2 (TRDOER2) in PWM Mode                                                            |     |

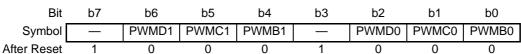

| 21.5.10 | Timer RD Output Control Register (TRDOCR) in PWM Mode                                                                     |     |

| 21.5.11 | Timer RD Control Register i (TRDCRi) (i = 0 or 1) in PWM Mode                                                             |     |

| 21.5.12 | Timer RD Status Register i (TRDSRi) (i = 0 or 1) in PWM Mode                                                              |     |

| 21.5.13 | Timer RD Interrupt Enable Register i (TRDIERi) (i = 0 or 1) in PWM Mode                                                   | 383 |

| 21.5.14 | Timer RD PWM Mode Output Level Control Register i (TRDPOCRi) (i = 0 or 1)                                                 | 202 |

| 21 5 15 | in PWM Mode  Timer PD Counter i (TPDi) (i = 0 or 1) in PWM Mode                                                           |     |

| 21.5.15 | Timer RD Counter i (TRDi) (i = 0 or 1) in PWM Mode                                                                        | 384 |

| 21.5.16 | Timer RD General Registers Ai, Bi, Ci, and Di (TRDGRAi, TRDGRBi, TRDGRCi, TRDGRDi) (i = 0 or 1) in PWM Mode               | 385   |

|---------|---------------------------------------------------------------------------------------------------------------------------|-------|

| 21.5.17 | Timer RD Pin Select Register 0 (TRDPSR0)                                                                                  |       |

| 21.5.17 | Timer RD Pin Select Register 1 (TRDPSR1)                                                                                  |       |

| 21.5.19 | Operating Example                                                                                                         |       |

| 21.5.20 | A/D Trigger Generation                                                                                                    |       |

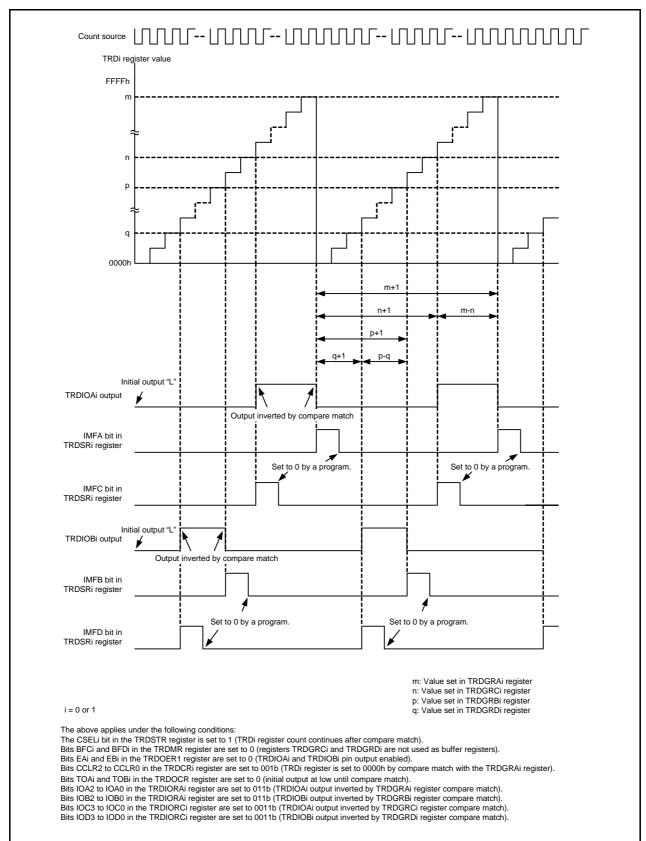

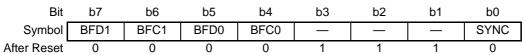

|         | eset Synchronous PWM Mode                                                                                                 |       |

| 21.6.1  | Module Standby Control Register (MSTCR)                                                                                   |       |

| 21.6.2  | Timer RD Control Expansion Register (TRDECR)                                                                              |       |

| 21.6.3  | Timer RD Trigger Control Register (TRDADCR)                                                                               |       |

| 21.6.4  | Timer RD Start Register (TRDSTR) in Reset Synchronous PWM Mode                                                            |       |

| 21.6.5  | Timer RD Mode Register (TRDMR) in Reset Synchronous PWM Mode                                                              |       |

| 21.6.6  | Timer RD Function Control Register (TRDFCR) in Reset Synchronous PWM Mode                                                 |       |

| 21.6.7  | Timer RD Output Master Enable Register 1 (TRDOER1) in Reset Synchronous PWM Mode                                          |       |

| 21.6.8  | Timer RD Output Master Enable Register 2 (TRDOER2) in Reset Synchronous PWM Mode                                          |       |

| 21.6.9  | Timer RD Control Register 0 (TRDCR0) in Reset Synchronous PWM Mode                                                        |       |

| 21.6.10 | Timer RD Status Register i (TRDSRi) (i = 0 or 1) in Reset Synchronous PWM Mode                                            | . 399 |

| 21.6.11 | Timer RD Interrupt Enable Register i (TRDIERi) (i = 0 or 1) in Reset Synchronous PWM Mode                                 | 400   |

| 21.6.12 | Timer RD Counter 0 (TRD0) in Reset Synchronous PWM Mode                                                                   | . 400 |

| 21.6.13 | Timer RD General Registers Ai, Bi, Ci, and Di (TRDGRAi, TRDGRBi, TRDGRCi, TRDGRDi)                                        |       |

|         | (i = 0 or 1) in Reset Synchronous PWM Mode                                                                                | 401   |

| 21.6.14 | Timer RD Pin Select Register 0 (TRDPSR0)                                                                                  | 402   |

| 21.6.15 | Timer RD Pin Select Register 1 (TRDPSR1)                                                                                  | 403   |

| 21.6.16 | Operating Example                                                                                                         | 404   |

| 21.6.17 | A/D Trigger Generation                                                                                                    | 405   |

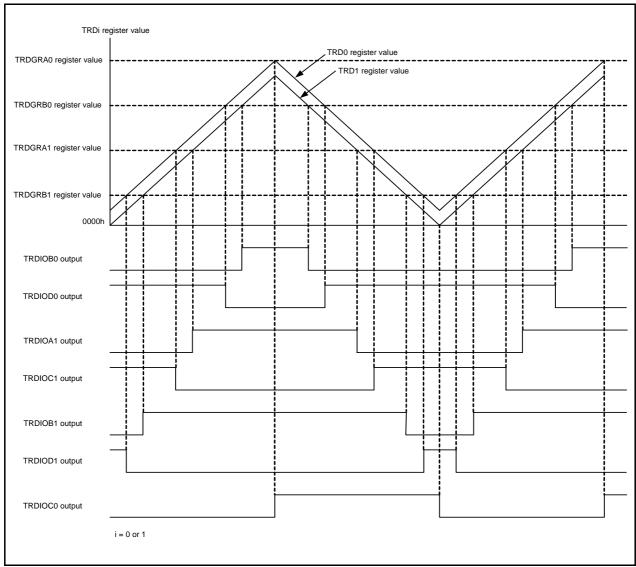

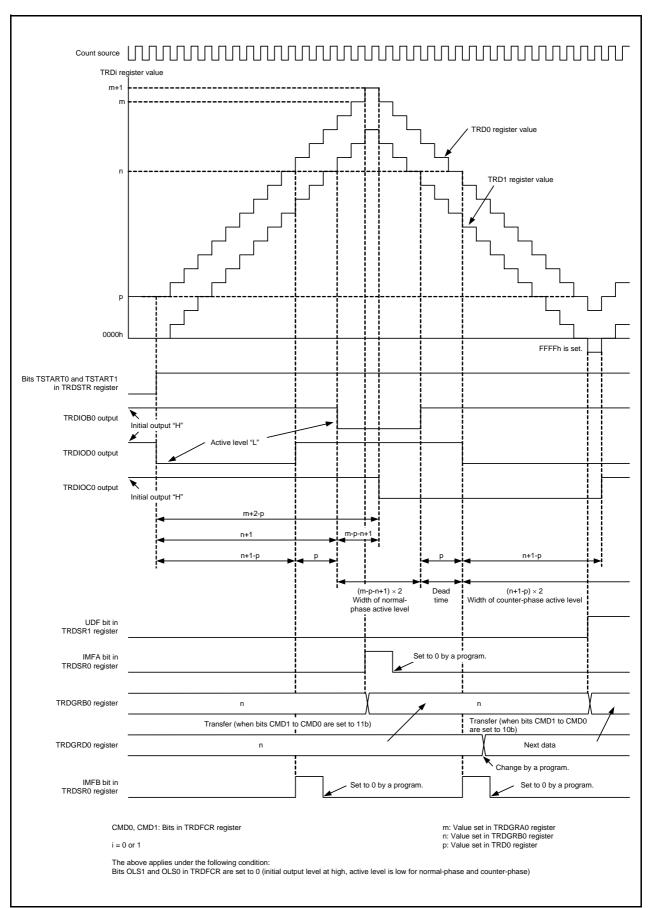

| 21.7 C  | omplementary PWM Mode                                                                                                     |       |

| 21.7.1  | Module Standby Control Register (MSTCR)                                                                                   |       |

| 21.7.2  | Timer RD Control Expansion Register (TRDECR)                                                                              |       |

| 21.7.3  | Timer RD Trigger Control Register (TRDADCR) in Complementary PWM Mode                                                     |       |

| 21.7.4  | Timer RD Start Register (TRDSTR) in Complementary PWM Mode                                                                |       |

| 21.7.5  | Timer RD Mode Register (TRDMR) in Complementary PWM Mode                                                                  |       |

| 21.7.6  | Timer RD Function Control Register (TRDFCR) in Complementary PWM Mode                                                     |       |

| 21.7.7  | Timer RD Output Master Enable Register 1 (TRDOER1) in Complementary PWM Mode                                              |       |

| 21.7.8  | Timer RD Output Master Enable Register 2 (TRDOER2) in Complementary PWM Mode                                              |       |

| 21.7.9  | Timer RD Control Register i (TRDCRi) (i = 0 or 1) in Complementary PWM Mode                                               |       |

| 21.7.10 | Timer RD Status Register i (TRDSRi) (i = 0 or 1) in Complementary PWM Mode                                                |       |

| 21.7.11 | Timer RD Interrupt Enable Register i (TRDIERi) (i = 0 or 1) in Complementary PWM Mode                                     |       |

| 21.7.12 | Timer RD Counter 0 (TRD0) in Complementary PWM Mode                                                                       |       |

| 21.7.13 | Timer RD Counter 1 (TRD1) in Complementary PWM Mode                                                                       |       |

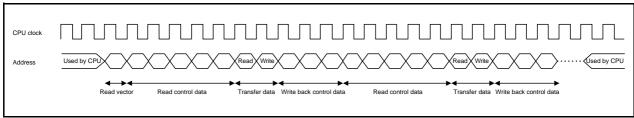

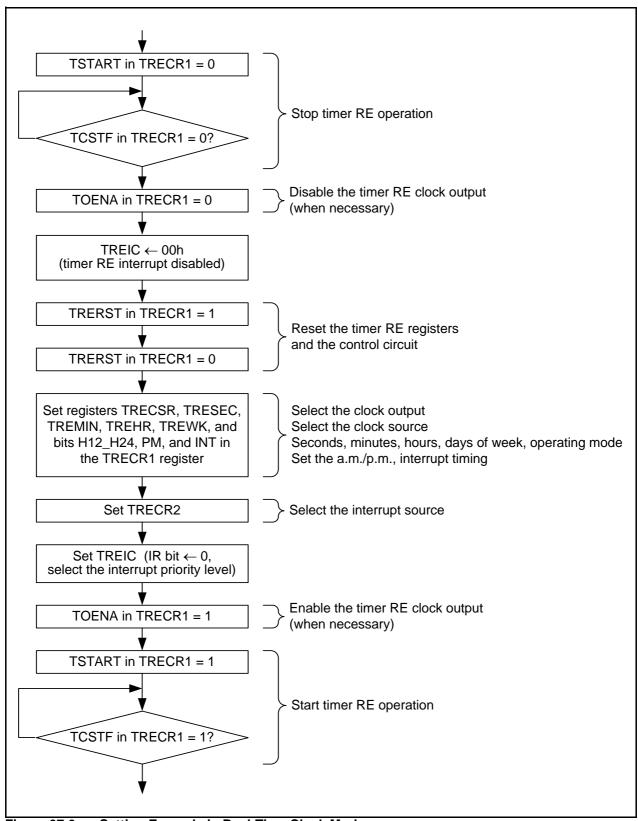

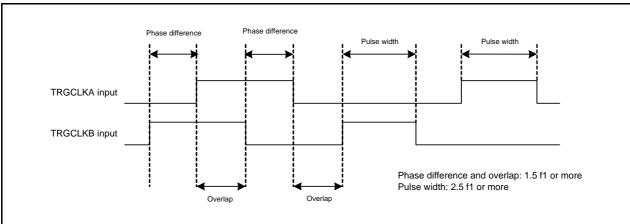

| 21.7.14 | Timer RD General Registers Ai, Bi, C1, and Di (TRDGRAi, TRDGRBi, TRDGRC1, TRDGRDi) (i = 0 or 1) in Complementary PWM Mode |       |